JK-тригери є найбільш універсальними. Мають два інформаційних входи: J і K. Функціонує подібно RS -тригер з різницею, що не має забороненої комбінації вхідних сигналів. На рис. 3.15, а дана таблиця переходів, з якої видно, що при подачі на обидва входи сигналу 1, на виході тригера змінюється стан на протилежне.

На основі JK -тригер реалізуються RS -, D - і Т -тригер. Якщо використовувати входи J і K. як входи S і R і виключити заборонену комбінацію, коли на обидва входи подано сигнал 1, то отримаємо RS- тригер. Якщо вхід До з'єднати з входом J інвертором, то отримаємо D -тригер (рис.3.15, в). Якщо на обидва входи: J і K - подати сигнал високого рівня (встановити 1) і використовувати вхід C для надходження сигналів, то отримаємо T -тригер.

Т-тригер (рис. 3.15, в,) змінює свій стан на протилежне при надходженні на вхід Т імпульсу, що запускає. Т -тригер називають тригерами з рахунковим входом. В інтегральному виконанні Т -тригер не випускаються, так як вони легко виходять з RS -, JK - або D -тригер (рис. 3.15, д).

Т-тригер - це рахунковий тригер. Т-тригер має один вхід (допоміжні входи примусової установки "0" і "1" не розглядаються), куди подають тактирующие (рахункові) імпульси. Після подачі кожного тактирующего імпульсу стан Т-тригера змінюється в протилежне (інверсне) попереднього стану (аналогічно стану JK-тригера при комбінації вхідних змінних J = 1 і K = 1). Т-тригери будуються тільки на базі двоступеневих (RS, D, JK) тригерів.

Т-тригер можна синтезувати з будь-якого типу двоступеневого тригера. Розглянемо приклад синтезу Т-тригера з JK-тригера. Для цього Т-тригер представимо як сукупність комбінаційного пристрою КУ і JK-тригера (рис. 3.19).

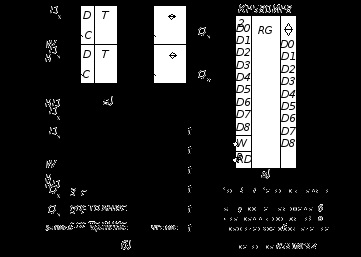

38. Паралельні та послідовні регістри на основі d-тригерів.

Регістри - пристрої, призначені для прийому зберігання та передачі інформації, представленої двійковим кодом. Кожному розряду двійкового коду відповідає певний розряд регістра. За допомогою регістрів можна виконувати деякі логічні операції, а також перетворювати інформацію одного виду в інший (наприклад, з послідовного коду в паралельний).

Регістр являє собою сукупність певним чином з'єднаних тригерних осередків з пристроєм управління вхідними та вихідними сигналами.

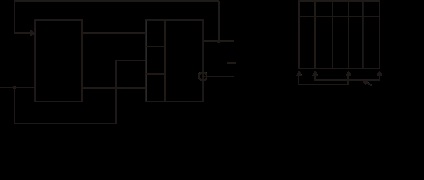

За способом введення і виведення (прийому і передачі) регістри поділяються на паралельні, послідовні і послідовно-паралельні. Регістри з паралельним прийомом і видачею інформації (регістри пам'яті) виконують на основі синхронних D- тригерів. На рис. 3.17 дана спрощена схема двох розрядів многоразрядного регістра пам'яті.

Надходить інформація в вигляді сукупності сигналів на входах (D0. D1 і т.д.) після видачі сигналу записи

У серійних регістрах пам'яті передбачаються більш складні схеми, що дозволяють очистити реєстр, організувати інверсію біт, забезпечити режими паралельного і послідовного введення інформації і т.д.

Последовательниерегістри (зсувні регістри) складаються з послідовного з'єднання тригерів. Під дією тактових імпульсів стан кожного тригера передається наступному, що рівносильно зрушення коду. Введення даних здійснюється синхронно під дією тактових імпульсів С.

Зсувні регістри дозволяють здійснювати логічну операцію зсуву коду записаного числа на будь-яку кількість розрядів. Зрушення застосовується для перетворення паралельного коду в послідовний і навпаки, для операцій множення і ділення (зрушення вліво на один розряд - це множення на два, вправо - поділ на два).

На рис. 3.18 представлена спрощена схема зсувного регістру. Поданий на вхід D першоготригера сигнал DR після надходження першого імпульсу на просуває шині З буде збережений в першому D -тригер і при необхідності його можна прочитати у вигляді сигналу Q0. При отриманні другого імпульсу на просуває шині З сигнал DR перенесуть в другій тригер і з'явиться на вході Q1. потім після третього імпульсу С - на виході Q і т.д.