Мікросхеми процесорів і шини 221

Нарешті, скидання сигналу MSYN викликає скидання сигналу SSYN, і на цьому процес зчитування закінчується.

Набір таких взаємообумовлених сигналів називається повним квитированием. Тут, по суті, спостерігається 4 події:

1. Установка сигналу MSYN.

2. Установка сигналу SSYN у відповідь на сигнал MSYN.

3. Скидання сигналу MSYN у відповідь на сигнал SSYN.

4. Скидання сигналу SSYN у відповідь на скидання сигналу MSYN.

Зрозуміло, взаємозумовленість сигналів не є синхронною. Кожна подія викликається попереднім подією, а не імпульсами генератора. Якщо якась пара пристроїв (задаючи і підпорядковане) працює повільно, це ніяк не впливає на іншу пару пристроїв, яка може працювати набагато швидше.

Переваги асинхронної шини очевидні, хоча насправді більшість шин є синхронними. Справа в тому, що синхронну систему побудувати простіше, ніж асинхронну. Центральний процесор просто видає сигнали, а пам'ять просто реагує на них. Тут немає жодного причинно-наслідкового зв'язку, а якщо компоненти вибрані вдало, все працює і без квитування. Крім того, в розробку синхронних шин вкладено дуже багато ресурсів.

До цього моменту ми неявно припускали, що існує тільки одне задає пристрій шини - центральний процесор. Насправді мікросхеми вводу-виводу можуть ставати задають пристроями при зчитуванні інформації з пам'яті і запису інформації в пам'ять. Крім того, вони можуть викликати переривання. Співпроцесори також можуть ставати задають пристроями шини. Виникає питання: «Що відбувається, коли задає пристроєм шини стають два або більше пристроїв одночасно?» Щоб запобігти хаосу, який може при цьому виникнути, потрібен спеціальний механізм - так званий арбітраж шини.

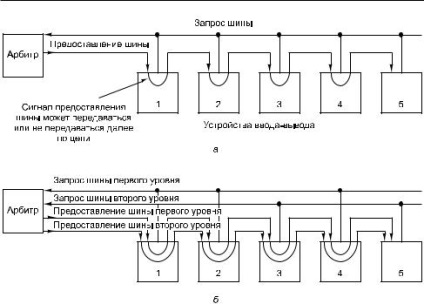

Арбітраж може бути централізованим або децентралізованим. Розглянемо спочатку централізований арбітраж. Простий приклад централізованого арбітражу показаний на рис. 3.37, а. В даному прикладі один арбітр шини визначає, чия черга наступна. Часто механізм арбітражу вбудовується в мікросхему процесора, але іноді використовується окрема мікросхема. Шина містить одну лінію запиту (монтажне АБО), яка може запускатися одним або декількома пристроями в будь-який час. Арбітр не може визначити, скільки пристроїв запитують шину. Він може визначити тільки факт наявності або відсутності запитів.

Коли арбітр виявляє запит шини, він встановлює лінію надання шини. Ця лінія послідовно пов'язує всі пристрої введення-виведення (як в ялинкової гірлянди). Коли фізично найближчим до арбітра пристрій отримує сигнал надання шини, цей пристрій перевіряє, чи немає запиту шини. Якщо запит є, пристрій користується шиною, але не поширює сигнал надання далі по лінії. Якщо запиту немає, пристрій передає сигнал надання шини наступного пристрою. Це пристрій теж про-

222 Глава 3. Цифровий логічний рівень

Мал. 3.37. Однорівневий централізований арбітраж шини з послідовним опитуванням (а); дворівневий централізований арбітраж (б)

Вірячи, чи є запит, і діє відповідним чином залежно від наявності або відсутності запиту. Передача сигналу надання шини триває до тих пір, поки який-небудь пристрій не скористається наданою шиною. Така система називається системою послідовного опитування. При цьому пріоритети пристроїв залежать від того, наскільки близько вони знаходяться до арбітра. Найближче до арбітра пристрій володіє найвищим пріоритетом.

Щоб пріоритети пристроїв не залежали від відстані від арбітра, в деяких шинах підтримується кілька рівнів пріоритету. На кожному рівні пріоритету є лінія запиту шини і лінія надання шини. На рис. 3.37, б зображено 2 рівня (хоча в дійсності шини зазвичай підтримують 4, 8 або 16 рівнів). Кожен пристрій пов'язано з одним з рівнів запиту шини, причому чим вище рівень пріоритету, тим більше пристроїв прив'язане до цього рівня. На рис. 3.37, б можна бачити, що пристрої 1, 2 і 4 мають пріоритет рівня 1, а пристрої 3 і 5 - пріоритетом рівня 2.

Якщо одночасно запитується кілька рівнів пріоритету, арбітр надає шину найвищому рівню. Серед пристроїв однакового пріоритету реалізується система послідовного опитування. На рис. 3.37, б видно, що в разі конфлікту пристрій 2 «перемагає» пристрій 4, а пристрій 4 «перемагає» пристрій 3. Пристрій 5 має нижчий пріоритет, оскільки воно знаходиться в самому кінці самого нижнього рівня.

Слід зауважити, що з технічної точки зору лінія надання шини рівня 2 не обов'язково повинна послідовно пов'язувати пристрої 1 і 2, оскільки вони не можуть посилати на неї запити. Однак набагато простіше

Мікросхеми процесорів і шини 223

провести всі лінії надання шини через всі пристрої, ніж з'єднувати пристрої особливим чином в залежності від їх пріоритетів.

Деякі арбітри містять третю лінію, яка встановлюється, як тільки пристрій приймає сигнал надання шини, і отримує шину в своє розпорядження. Як тільки ця лінія підтвердження прийому встановлюється, лінії запиту і надання шини можуть бути скинуті. В результаті інші пристрої можуть запитувати шину, поки перший пристрій її використовує. До того моменту, коли закінчиться поточна передача, наступне задає пристрій вже буде вибрано. Це пристрій може почати роботу, як тільки буде скинута лінія підтвердження прийому. З цього моменту починається наступний цикл арбітражу. Така структура вимагає додаткової лінії і більшої кількості логічних схем в кожному пристрої, але зате при цьому цикли шини використовуються раціональніше.

В системах, де пам'ять пов'язана з головною шиною, центральний процесор повинен конкурувати з усіма пристроями введення-виведення практично на кожному циклі шини. Щоб вирішити цю проблему, можна надати центральному процесору найнижчий пріоритет. При цьому шина буде надаватися процесору тільки в тому випадку, якщо вона не потрібна жодному іншому пристрою. Центральний процесор завжди може почекати, а пристрої введення-виведення повинні отримати доступ до шини якомога швидше, щоб не втратити дані. Наприклад, диски, що обертаються з високою швидкістю, не можуть чекати. У багатьох сучасних комп'ютерах для вирішення цієї проблеми пам'ять поміщається на одну шину, а пристрої введення-виведення - на іншу, тому їм не доводиться завершувати роботу, щоб надати доступ до шини.

Можливий також децентралізований арбітраж шини. Наприклад, комп'ютер може містити 16 пріоритетних ліній запиту шини. Коли пристрою потрібна шина, воно встановлює свою лінію запиту. Всі пристрої відстежують всі лінії запиту, тому в кінці кожного циклу шини кожен пристрій може визначити, чи володіє воно в даний момент найвищим пріоритетом і, отже, дозволено їй користуватися шиною в наступному циклі. Такий метод вимагає більшої кількості ліній, але зате позбавляє від потенційних витрат ресурсів на використання арбітра. У цьому випадку число пристроїв обмежується числом ліній запиту.

При іншому типі децентралізованого арбітражу використовуються тільки три лінії незалежно від того, скільки пристроїв є в наявності (рис. 3.38). Перша лінія - монтажне АБО. Вона потрібна для запиту шини. Друга лінія називається BUSY і означає зайнятість. Вона запускається поточним задає пристроєм шини. Третя лінія служить для арбітражу шини. вона

Мал. 3.38. Децентралізований арбітраж шини

224 Глава 3. Цифровий логічний рівень

послідовно з'єднує всі пристрої. Початок ланцюга пов'язане з джерелом живлення з напругою 5 В.

Коли шина не потрібно жодному з пристроїв, лінія арбітражу передає сигнал всім пристроям. Щоб отримати доступ до шини, пристрій спочатку перевіряє, чи вільна шина і встановлений сигнал арбітражу IN. Якщо сигнал IN не встановлено, пристрій не може стати задає пристроєм шини.

У цьому випадку воно скидає сигнал OUT. Якщо сигнал IN встановлено, пристрій також скидає сигнал OUT, в результаті чого наступний пристрій не отримує сигналу IN і, в свою чергу, скидає сигнал OUT. Отже, все наступні по ланцюгу пристрою не отримують сигнал IN і скидають сигнал OUT.

В результаті залишається тільки один пристрій, у якого сигнал IN встановлено, а сигнал OUT скинутий. Воно стає задає пристроєм шини, встановлює лінію BUSY і сигнал OUT, після чого починає передачу даних.

Трохи поміркувавши, можна виявити, що з усіх пристроїв, яким потрібна шина, доступ до шини отримує саме ліве. Така система нагадує систему послідовного опитування, тільки в даному випадку немає арбітра, тому вона коштує дешевше і працює швидше. До того ж не виникає проблем зі збоями арбітра.

Принципи роботи шини

До цього моменту ми обговорювали тільки звичайні цикли шини, коли задає пристрій (зазвичай центральний процесор) зчитує інформацію з підлеглого пристрою (зазвичай з пам'яті) або записує в нього інформацію. Однак існують ще кілька типів циклів шини. Давайте розглянемо деякі з них.

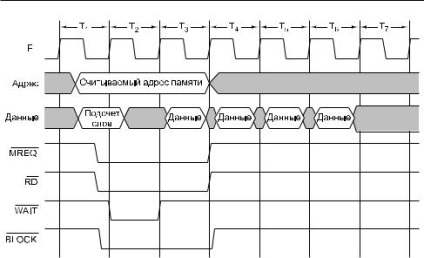

Зазвичай за раз передається одне слово. При використанні кеш-пам'яті бажано відразу викликати всю рядок кеш-пам'яті (тобто 16 послідовних 64-розрядних слів). Однак часто передача блоками може бути більш ефективна, ніж така послідовна передача інформації. Коли починається читання блоку, що задає пристрій повідомляє підлеглому пристрою, скільки слів потрібно передати (наприклад, поміщаючи загальне число слів на інформаційні лінії в період T 1). Замість того щоб видати у відповідь одне слово, задає пристрій видає одне слово протягом кожного циклу до тих пір, поки не буде передано необхідну кількість слів. На рис. 3.39 з Браж така ж схема, як і на рис. 3.35, тільки з додатковим сигналом BLOCK, який вказує, що запитується передача блоку. В даному прикладі зчитування блоку з чотирьох слів займає 6 циклів замість 12-ти.

Існують також інші типи циклів шини. Наприклад, якщо мова йде про системи з двома або кількома центральними процесорами на одній шині, потрібно бути впевненим, що в конкретний момент тільки один центральний процесор може використовувати певну структуру даних в пам'яті. Щоб упорядкувати цей процес, в пам'яті повинна міститися змінна, яка приймає значення 0, коли центральний процесор використовує структуру даних, і 1, коли структура даних не використовується. Якщо центрального процесора потрібно отримати доступ до структури даних, він повинен вважати змінну, і якщо вона дорівнює 0, надати їй значення 1. Проблема полягає в тому, що два

Мікросхеми процесорів і шини 225

Мал. 3.39. Передача блоку даних

центральних процесора можуть зчитувати змінну на послідовних циклах шини. Якщо кожен процесор виявить, що змінна дорівнює 0, а потім змінить значення змінної на 1, як ніби тільки він один використовує цю структуру даних, то така послідовність подій призведе до хаосу.

Щоб не допустити подібну ситуацію, в мультипроцесорних системах передбачений спеціальний цикл шини, який дає можливість будь-якому процесору вважати слово з пам'яті, перевірити і змінити його, а потім записати назад в пам'ять; весь цей процес відбувається без звільнення шини. Такий цикл не дає можливості іншим центральним процесорам використовувати шину і, отже, заважати роботі першого процесора.

Ще один важливий цикл шини - цикл обробки переривань. Коли центральний процесор командує пристрою введення-виведення зробити якусь дію, він очікує переривання після завершення роботи. Для сигналу переривання потрібна шина.

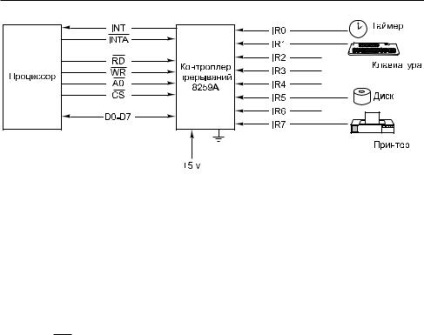

Оскільки може скластися ситуація, коли кілька пристроїв одночасно захочуть виконати переривання, тут мають місце ті ж проблеми вирішення конфліктних ситуацій, що і в звичайних циклах шини. Щоб уникнути таких проблем, потрібно кожному пристрою приписати певний пріоритет і для розподілу пріоритетів підтримувати централізований арбітраж. Для цих цілей існує стандартний, широко використовуваний інтерфейс переривань. У комп'ютерах IBM PC і наступних моделях для цього служить мікросхема Intel 8259A. Вона зображена на рис. 3.40.

До восьми контролерів вводу-виводу можуть бути безпосередньо пов'язані з вісьмома входами IR x (Interrupt Request - запит переривання) мікросхеми 8259A. Коли будь-яка з цих пристроїв вирішить провести переривання, воно запускає свою лінію входу. При активізації одного або декількох входів контролер 8259A видає сигнал INT (INTerrupt - переривання), який подається

226 Глава 3. Цифровий логічний рівень

Мал. 3.40. Контролер переривань 8259A

Мікросхема 8259A містить кілька регістрів, які центральний процесор може зчитувати і зап ісивать, використовуючи про ичние цикли шини та висновки RD (ReaD - читання), WR (WRite - запис), CS (Chip Select - вибір елемента пам'яті) і A0. Коли програмне забезпечення опрацювало переривання і готово отримати наступне, воно записує спеціальний код в один з регістрів, який викликає скидання сигналу INT мікросхемою 8259A, якщо не з'являється інше переривання. Регістри також можуть записуватися для того, щоб перевести мікросхему 8259A в один з декількох режимів, і для виконання деяких інших функцій.

При наявності більше 8 пристроїв введення-виведення, мікросхеми 8259A можуть з'єднуватися каскадом. У самій екстремальній ситуації все 8 входів можуть бути пов'язані з виходами ще 8 мікросхем 8259A, поєднуючи до 64 пристроїв введення-виведення в двоступеневу систему обробки переривань. Контроллерконцентратор введення / виведення Intel ICH10 I / O, одна з мікросхем чіпсета Core i7, містять два контролера переривань 8259A. Таким чином, ICH10 має 15 зовнішніх переривань - на 1 менше 16 переривань двох контролерів 8259A, так як одне з переривань використовується для каскадного підключення другого контролера 8259A. Мікросхема 8259A містить кілька висновків для каскадного з'єднання, але ми їх опустили заради простоти. В наші дні 8259A є складовою частиною іншого мікросхеми.

Хоча наведене опис жодним чином не вичерпує всіх питань розробки шин, воно дає достатньо інформації для загального розуміння принципів роботи шини і принципів взаємодії з шиною центрального процесора. Тепер ми перейдемо від загального до приватного і розглянемо кілька конкретних прикладів процесорів і їх шин.