Every people has right on left

Chia ulo havas rajton sur levo

Кожна людина має право на ліво

(Н. Фоменко)

B.2. SRAM і DRAM.

Напівпровідникова оперативна пам'ять у даний час поділяється на статичне ОЗУ (SRAM) і динамічне ОЗУ (DRAM). Перш, ніж пояснювати різницю між ними, розглянемо еволюцію напівпровідникової пам'яті за останні сорок років.

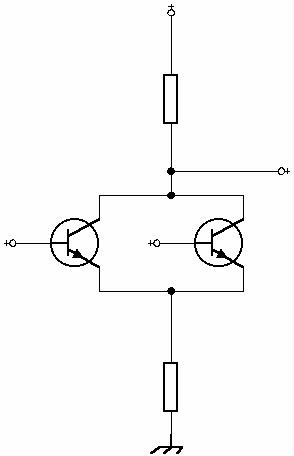

B.2.1. Тригери.

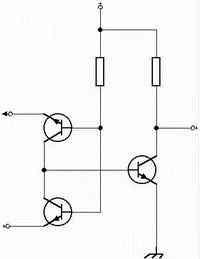

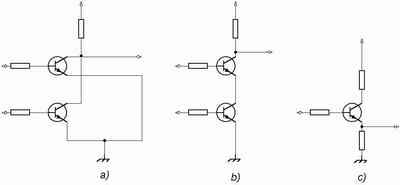

B.2.2. Елементна база логіки.

Як видно з цього огляду, логіка на біполярних транзисторах найшвидша, але одночасно найдорожча і володіє високою потужністю розсіювання (і значить - краще "гріється".) За інших рівних умов логіка на польових транзисторах більш повільна, але володіє меншим електроспоживанням і меншою вартістю .

B.2.3. SRAM. Зауваження.

З попереднього розділу Ви дізналися, що є елементної базою статичного ОЗУ. Як Ви вже зрозуміли, статичне ОЗУ - дорогий і неекономічний вид ОЗУ. Тому його використовують в основному для кеш-пам'яті, регістрах мікропроцесори і системах управління RDRAM (дивись розділ B.3.3.5).

B.2.4. DRAM. Що це таке?

Для того, щоб здешевити оперативну пам'ять, в 90-х роках XX століття замість дорогого статичного ОЗУ на тригерах стали використовувати динамічне ОЗУ (DRAM). Принцип пристрою DRAM наступний: система метал-діелектрик-напівпровідник здатна працювати як конденсатор. Як відомо, конденсатор здатний деякий час "тримати" на собі електричний заряд. Позначивши "заряджену" стан як 1 і "незаряджені" як 0, ми отримаємо осередок пам'яті ємністю 1 біт. Оскільки заряд на конденсаторі розсіюється через деякий проміжок часу (який залежить від якості матеріалу і технології його виготовлення), то його необхідно періодично "заряджати" (регенерувати), зчитуючи і знову записуючи в нього дані. Через це і виникло поняття "динамічна" для цього виду пам'яті.

За 10 років, що минули з часу створення перших мікросхем DRAM, їхній розвиток йшло «семимильними» кроками в порівнянні з SRAM. Еволюція DRAM розглядається в наступному підрозділі.