Напівпровідникові ІС виготовляються шляхом формування в монокристаллическом тілі напівпровідника структури ІС за допомогою технологічних операцій. Створюються різні області, що володіють доречний (р- область) та електронної (n-область) проводимостями. Освічені області в напівпровіднику відповідають за своїми функціями певних елементів: активним (транзистор, діод) і пасивним (резистор, конденсатор і ін.). Об'ємні струмопровідні доріжки створюються нанесенням на поверхню напівпровідника інверсного шару високої провідності. Така напівпровідникова ІС може являти собою закінчену конструкцію мікроелектронного вироби, тобто конструкцію електричного кола, безпосередньо реалізує параметри і характеристики цього ланцюга.

Виконання і оформлення конструкторської документації напівпровідникових ІС регламентуються стандартами ЕСКД і галузевими стандартами. В основний комплект конструкторської документації на ІС входять специфікація, принципова електрична схема (ЕЗ), топологічні складальні і пошарові креслення вироби (СБ). патентний формуляр (ПФ), карта технологічного рівня і якості виробу

(КУ), довідковий лист (Д1) і етикетка 07).

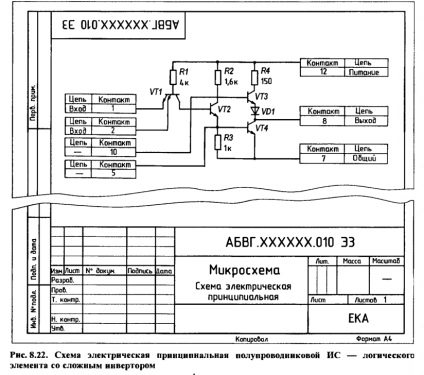

Процес конструювання мікросхеми починають з розробки схеми електричної принципової (ЕЗ). На рис. 8.22 представлена схема логічного елемента транзисторних-транзисторної логіки зі складним інвертором. Всі елементи мають графічні буквено-цифрові позначення відповідно до ГОСТ ЕСКД. Транзистори зображені без корпусу. Буквено-цифрові позначення присвоєні всім елементам послідовно незалежно від конструкції елемента (напівпровідниковий, навісний, плівковий). Виходи, входи і контакти харчування в схемі розташовують в ряд, в даному випадку - вертикально. Поруч з умовним графічним позначенням елементів вказують номінали, допуски та інші дані. Перелік елементів при цьому не розробляють. На підставі електричної принципової схеми розробляють топологічний креслення на декількох аркушах. Топологічні креслення виконують в масштабі збільшення 100: 1; 200: 1; 400: 1, що дозволяє отримати наочне розташування елементів. На першому аркуші (основний вид) зображують підкладку з усіма нанесеними шарами (елементами).

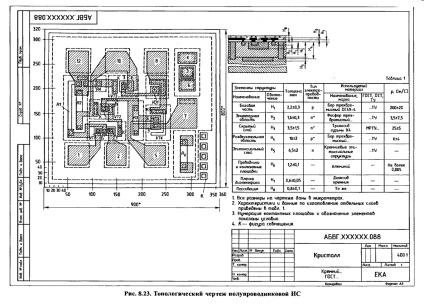

На зображенні підкладки повинні бути виконані фігури суміщення, є технологічними (рис. 8.23). Фігури суміщення можуть бути різної форми: трикутної, прямокутної, хрестової і ін. Відповідні фігури суміщення показують і на окремих шарах. Контактні майданчики виконують у вигляді багатокутників, заштриховують і нумерують їх, починаючи з лівого нижнього кута проти напрямку годинникової стрілки. Внутрішні майданчики нумерують зверху вниз і зліва направо. Для зручності креслення елементів мікросхеми на топологічних кресленнях використовують координатну сітку з кроком 0,01; 0,05; 0,1 або 0,2 мм. Вершини фігур елементів необхідно розташовувати в точках перетину ліній сітки. На кресленні сітка не показується, а по периметру наносяться значення координат. Крім виконавчих повинні бути вказані габаритні розміри для довідок.

На першому аркуші топологічного креслення виконується складний ступінчастий розріз через різні елементи і компоненти (положення січної площини не позначається). Товщина шарів позначається буквою Н з відповідним цифровим індексом. Масштаб товщини шарів для наочності допускається не витримувати. Основні дані шарів ІС вказують в таблиці на полі креслення. Таблиця може містити такі графи: «Елементи

структури »,« Тип електричної провідності »,« Матеріал, що використовується »і ін. (див. рис. 8.23). Відомості про технологію виготовлення ІС вказують в технічних вимогах на полі креслення.

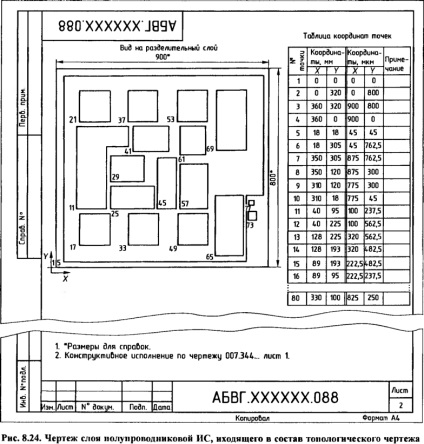

Наступні листи топологічного креслення виконують окремо для кожного шару, включаючи зображення сполучних провідників і контактних майданчиків. На рис. 8.24 представлений другий лист топологічного креслення кристала. Над зображенням шару повинна бути поміщений напис по типу «Вид на розділовий шар», «Вид на базовий шар» і т.п. Розміри елементів задаються за допомогою координатної сітки і таблиці координат.

Кожен елемент ІС (багатокутник) повинен мати цифрове позначення лівої нижньої вершини. Цифра 1 присвоюється лівому нижньому кутку прямокутника, що визначає межі кристала. Решта вершини прямокутника не означає, але мається на увазі їх нумерація за годинниковою стрілкою, і в таблиці координат приводяться значення всіх точок прямокутника (див. Рис. 8.24). Прямокутник, який визначає габарити кристала, заданий чотирма точками (1. 4). Наступні вершини позначаються послідовно для кожного елемента по розташуванню елементів зліва направо і знизу вгору. Основний напис на наступних аркушах виконується за формою 2а ГОСТ 2.104-68 *.

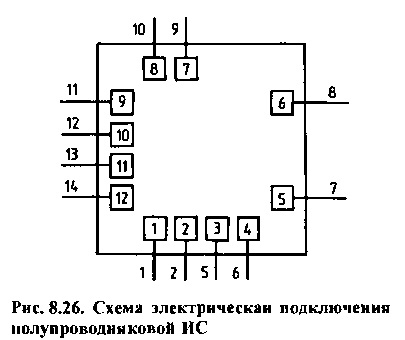

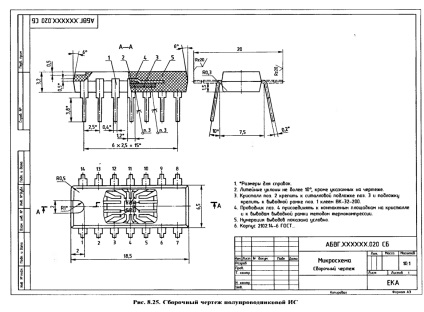

Матеріал шару дається в таблиці на першому аркуші топологічного креслення. Після виконання топологічних креслень всіх верств приступають до оформлення складального креслення (рис. 8.25). Креслення оформляють відповідно до вимог ГОСТ 2.109-73 * і галузевих стандартів. У технічних вимогах вказують відомості, необхідні для здійснення збирання і контролю вироби, параметри, що виконуються або підлягають контролю за даним кресленням, відомості про характер з'єднання складових частин мікросхеми, герметизації, маркування та ін. Специфікація

виконується відповідно до вимог ГОСТ 2.106-96. На складальних кресленнях з'єднання кристала з висновками на корпус не показують, а складають електричну схему підключення (рис. 8.26). Решта конструкторські документи - габаритний креслення, карта технологічного рівня і якості, патентний формуляр, етикетка та ін. - виконуються відповідно до стандартів ЕСКД.