Для підвищення розрядності центральний процесор складається з декількох секцій.

Незважаючи на те, що в даний час випуск секціонованих процесорів припинений, їх розгляд дозволить глибше зрозуміти принципи побудови і функціонування сучасних однокристальних мікропроцесорів і систем, побудованих на їх основі. Надалі розглядається Секціонірованние мікропроцесор К584.

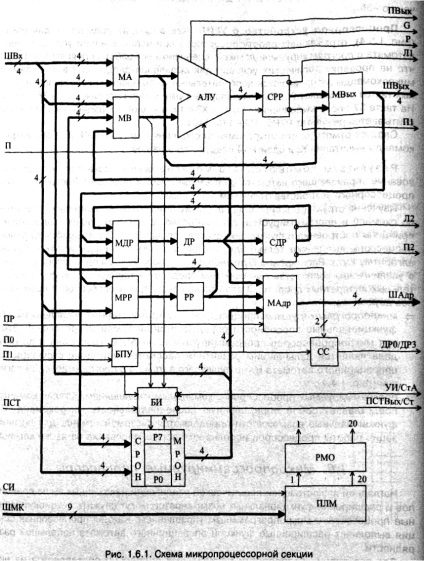

Структурно-функціональна організація процесора. Структурна схема окремої мікропроцесорної секції зображена рис. 1.6.1.

До складу секції входять наступні вузли:

● арифметичне-логічний пристрій (АЛП). призначене для виконання восьми арифметичних і восьми логічних операцій. На входи АЛП надходять операнди А, В і сигнал П перенесення АЛУ. З виходів АЛП знімаються результати операцій над операндами А, В, а також вихідний сигнал ПВих перенесення АЛУ і сигнали G, Р для прискореного перенесення;

● робочий регістр (РР). виконує основні функції при обробці інформації;

● додатковий регістр (ДР). або робочий регістр розширення, який використовується при операціях з подвійною точністю,

● блок регістрів загального призначення (POH). що складається з восьми регістрів Р0. Р7, призначених для зберігання та обміну інформацією між блоками секцій. Регістр Р7 зазвичай використовується для виконання функцій лічильника, який забезпечує Послідовність виконання команд: при збільшенні вмісту лічильника на +1 виконується наступна мікрокоманда; при збільшенні на +2 наступна мікрокоманда пропускається; режим відсутності рахунку використовується для занесення нового вмісту в Р7, що необхідно для реалізації переходів;

● блок позиційного управління (БПУ). вносить необхідні зміни в роботу секції в залежності від займаної нею позиції (молодшої, середньої, старшої) в процесорі, складеному з декількох секцій. Необхідна позиція секції встановлюється за допомогою сигналів П1, П0;

● сдвігатель робочого і додаткового регістром (CРР, СДР) при використанні сигналів БПУ дозволяють виконати операції зсуву вмісту зазначених регістрів;

● схема селекції (СС), що здійснює вибір розрядів додаткового регістра ДР в залежності від позиції, яку займає секцією. З її двох-функціональній вихідний лінії знімається молодший (ДРВ) або старший (ДРЗ) розряди вмісту ДР;

● блок інкрементора (БІ), призначений для зміни вмісту лічильника команд лічильника в залежності від значень сигналів перенесення на вході лічильника (ПСТ) і управління інкрементором (УІ), що надходять на їх вхід. З виходу блоку інкрементора БІ знімаються вихідний сигнал перенесення лічильника (ПСТВих) і старші розряди операндів А (ста) і В (СТВ). Режими роботи схеми селекції СС і блоку інкрементора БІ координуються сигналами П1, П0, які надходять на вхід блоку позиційного управління БПУ (табл. 1.6.1). За допомогою сигналів, що надходять на вхід БІ, встановлюється режим роботи регістра Р7 - лічильник або POH (табл. 1.6.2);

● мультіплексорA (MA) управляє проходженням операндів А з POH або вхідний шини (ШВХ) на вхід АЛП або вихідну шину (ШВих). Вхідна і вихідна шини складені з 4-х ліній;

● мультиплексор В (MB) управляє проходженням операндів В з РР, ДР або ШВХ на вхід АЛП; вихідний мультиплексор (Мвих) здійснює передачу операнда А, а також операндів з виходу АЛП на ШВих або входи РР, ДР, POH;

● програмована логічна матриця (ПЛМ) перетворює 9-розрядний код мікрокоманд, який надходить в секцію по шині микрокоманд (ШМК), складеної з 9-ї ліній, в 20-розрядний внутрішнє керуюче слово, що забезпечує управління роботою всіх блоків мікропроцесорної секції;

● регістр микроопераций (РМО), що складається з 20- і D -тригер, призначений для запам'ятовування внутрішнього керуючого слова на час виконання мікрокоманд. Використання регістра микроопераций РМО, завантаження якого проводиться по позитивному фронту синхроимпульса (при зміні сигналу з 0 в 1), дозволяє під час виконання поточної мікрокоманд виробляти в ПЛМ прийом і перетворення коду наступної мікрокоманд.

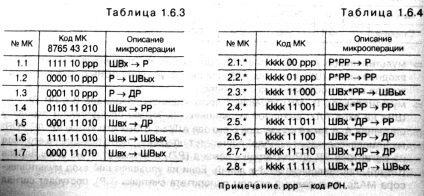

Система микрокоманд. Код мікрокоманд складається з дев'яти розрядів (К8 ÷ К0). Використовується два формати коду мікрокоманд:

● перший формат містить операційне поле з 4 старших розрядів К8 ÷ К5, що визначає в основному функції АЛУ; додаткове поле з розрядів К4 і КЗ. розширює можливості кодування; селекторну поле з трьох молодших розрядів К2 ÷ К0 (ррр), що дозволяє вибрати один з восьми POH, який бере участь в виконуваної мікрооперації;

● другий формат складається з одного поля, що містить всі розряди К8 ÷ К0 коду МК.

Для зручності користування система микрокоманд розбивається на шість груп. Розглянемо особливості МК кожної групи.

Група 1. За допомогою МК цієї групи (табл. 1.6.3) виконуються МО пересилання між внутрішніми вузлами МПС без участі АЛУ. Джерелом інформації є POH (Р) або ШВХ, приймачем - POH (Р), РР, ДР або ШВих.

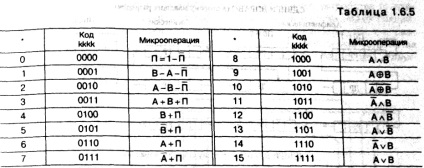

Група 2. До цієї групи (табл. 1.6.4) включені арифметичні і логічні операції, що виконуються АЛП. Операції, зазначені в табл. 1.6.4 зірочкою (*), залежать від коду kkkk і наведені в табл. 1.6.5. Ці операції виконуються в загальному випадку над операндами А, В, які надходять в АЛУ відповідно через мультиплексори А, В (рис. 1.6.1), з джерел зазначених в графі «Опис микрооперации» табл. 1.6.4 (ліва колонка відноситься до операнду А, а права - до операнду В).

Слід виділити три види операцій (табл. 1.6.5).

Операції над двома операндами. До них відносяться три (1-3) арифметичних і всі вісім (8-15) логічних операцій.

Операції над одним операндом. Ці операції (4-7) дозволяють виконати передачу через АЛУ прямого, зворотного або додаткового коду операндів А і В, а також пересилання з приростом: А + 1, В + 1.

Операції без участі операндів. Операцію П = 1 - ¯П можна використовувати для установки нулів і одиниць у всіх розрядах будь-якого з чотирьох приймачів інформації: Р, РР, ДР, ШВих.

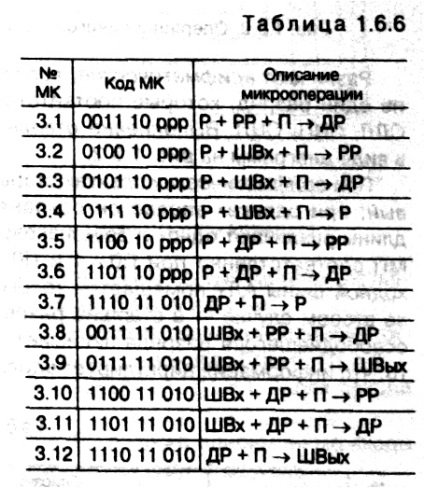

Група 3. Операції цієї групи (табл. 1.6.6) дозволяють виконати додавання, комбінуючи джерела (Р, РР ДР, ШВХ) і приймачі (Р, РР, ДР, ШВих) інформації. Операції ДР + П (3.7, 3.12) фактично є пересильних і доповнюють операції групи 1, причому є можливість інкрементіровать вміст додаткового регістра ДР.

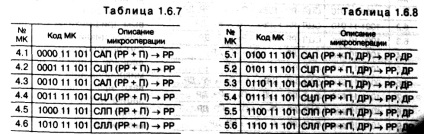

Групи 4, 5. Ці операції (табл. 1.6.7 та 1.6.8) дозволяють реалізувати повний набір зрушень вмісту, робочого регістра (РР) або регістра подвійної довжини (РР, ДР), складеного з послідовного з'єднання РР і ДР. В останньому випадку можливе суміщення зсуву з подсуммірованіем сигналу перенесення П в РР.

Розрізняють арифметичні, логічні і циклічні зрушення вправо і вліво на один розряд, які відповідно мають позначення: САП, САЛ, СЛП, СДЛ, СЦП, СЦЛ. Виконує окремі операції зрушень проілюстровано у вигляді діаграм на рис. 1.6.2.

При арифметичних зрушення старший (лівий) розряд використовується як знаковий; при зрушеннях вправо він зберігається. При роботі з операндами подвійної довжини розрізняють одно- і двухзнаковие зрушення, які реалізуються в старшій позиції МП відповідно при П0 = 1 і П0 = 0. У першому випадку старший розряд вихідний шини АЛП поміщається тільки в старший розряд робочого регістра РР, у другому випадку - в старші розряди РР і ДР. При логічних зрушення місце звільненого розряду займає нуль. Для циклічних зрушень характерно о, що інформація циркулює вздовж регістрів, не залишаючи їх.

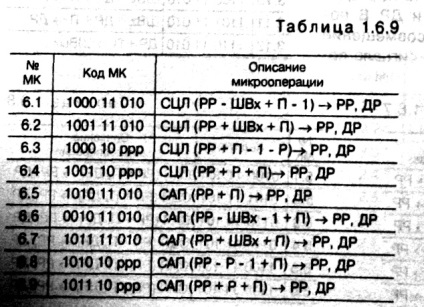

Група 6. Операції цієї групи (табл. 1.6.9) дозволяють виконати додавання чи віднімання при активному сигналі перенесення П в поєднанні з правим арифметичним або лівим циклічним зрушенням результату в регістрі подвійної довжини РР, ДР Ці микрооперации забезпечують ефективну реалізацію алгоритмів множення і ділення двійкових чисел.

Рекомендуйте цю статтю іншим!