Програма на vhdl вже є, тепер розповім що з нею робити.

При запуску програма пропонує створити новий проект або відкрити існуючий

вибираємо "Create a New Project", якщо вже зайшли в програму, тоді

File-> New Project Wizard ...

Не думаю що ви побачите щось нове: вибір каталогу і назва проекту, додавання файлів до проекту, вибір чіпа, фініш.

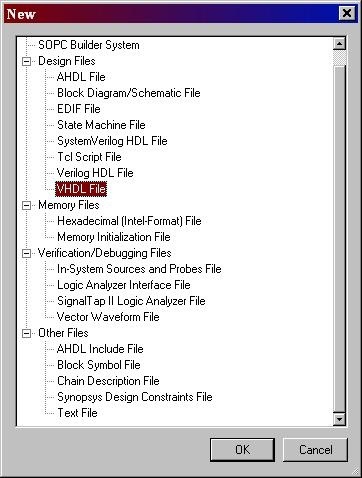

Тепер потрібно створити файл (грунтуючись на статтю Що таке VHDL. Найпростіший приклад створення логічного елемента в ПЛІС) створюємо файл vhdl

File-> New-> VHDL File

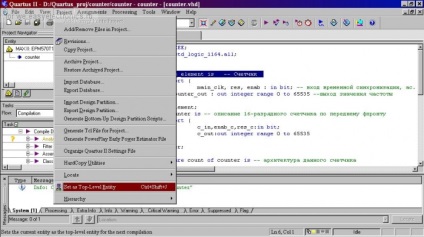

Копіпаст в нього весь код, зберігаємо. Тепер вказуємо програмі що це головний файл проекту

Project-> Set as Top-Level Entity

(Без цього нічого не вийде).

Можна компілювати.

Processing-> Start Compilation (Ctrl + L)

або фіолетовий трикутник вгорі на панелі.

Виводиться звіт про компіляції, якщо все добре - йдемо далі.

Перед прошивкою потрібно призначити відповідність між сигналами входу і виходу в проекті і пинами чіпа. заходимо

Assignments-> Pins

Внизу бачимо назву наших сигналів. В поле Location просто вибираємо потрібний пін, або клацнути два рази на піне (де зображення мікросхеми) і вибрати потрібне ім'я.

У ПЛІС все Піни рівноправні, можуть бути як входом, так і виходом, або двонаправлені. Деякі висновки можуть бути джерелом глобального клок, глобальним скиданням або глобальним enable. У нашому проекті є всі ці види сигналів, звичайно не обов'язково їх підключати до цих пінам, але в більшій проект де тактовий сигнал йде на багато модулів це буде ефективніше, оскільки фізично вони так побудовані всередині чіпа. Також в залежності від конкретної мікросхеми можна вибирати навантажувальну здатність виведення, підключати підтягаючий резистор або захисний діод.

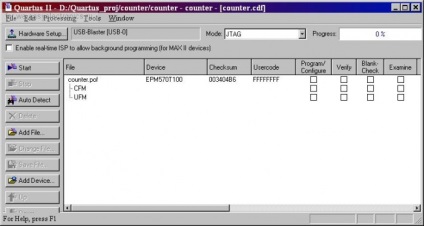

Після призначень висновків можна приступати до програмування

Tools-> Programmer

Коли проект складається з безлічі файлів (а це найчастіше), тоді зручно щоб головним був файл схемотехнического опису. створюємо

File-> New-> Block Diagram / Schematic File

Зберігаємо, назвемо його main.

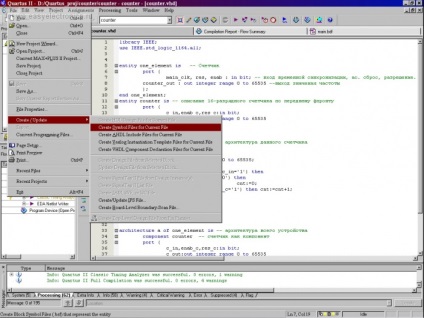

Щоб додати туди наш vhdl файл, треба створити з нього символьний файл. Для цього вибираємо vhdl файл, тиснемо

File-> Create / Update-> Create Symbol File for Current File

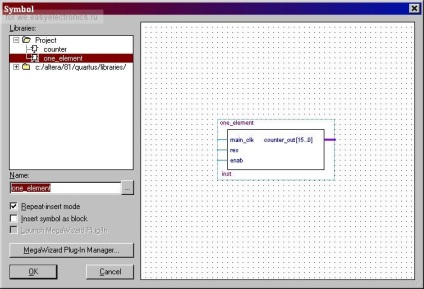

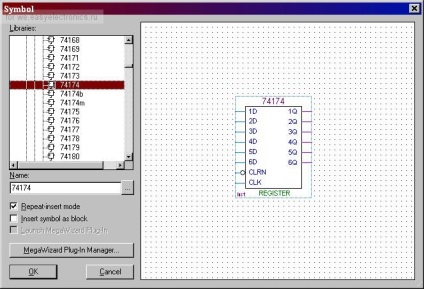

Повертаємося до нашого main.bdf, тиснемо Symbol Tool (кнопочка у вигляді логічного елемента І).

Програма створила 2 символьних файлу, оскільки в vhdl два entity. Власне то що ми описали в entity ми бачимо в образі цього символьного файлу, якийсь чорний ящик у якого є входи і виходи, а то що в ньому відбувається описано в architecture.

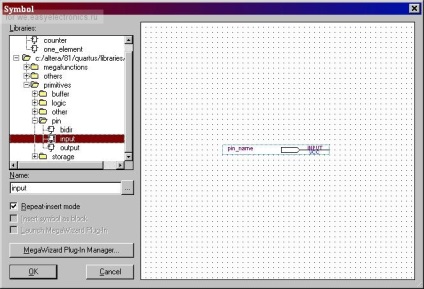

Тепер додаємо Піни, даємо їм якесь осмислене назва.

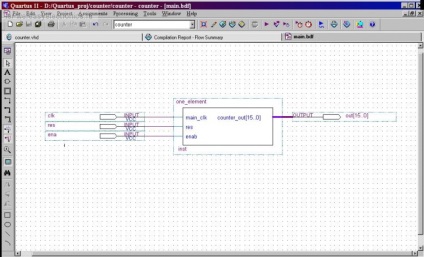

Має вийти щось типу цього:

Тут можна додавати різні цікаві штуки, такі як мікросхеми стандартної логіки або різні суматори, мультиплексори і т. Д.

Також в залежності від використовуваної мікросхеми її «фарш» у вигляді пам'яті, або як в сімействі MAX II, вбудований генератор на 5 МГц. Все додається і з'єднується проводами, причому в чіпі воно також буде фізично з'єднане.

Зберігаємо файл, знову проробляємо

Project-> Set as Top-Level Entity

Тепер мої зауваження і доопрацювання проекту.

Тут 2 entity будуть зайвими, оскільки в схемотехническом файлі можна з'єднувати всі блоки звичним чином і одні сигнал пускати куди завгодно.

Також тут не потрібно підключати бібліотеку, т. К. Вона не використовується (в ній описані сигнали типу std_logic).

Наш файл спрощується до такого

тепер внесу свої 5 копійок в код

відмазки

Історично склалося що я описав створення проекту в Квартус за першою статтею про vhdl, хоча краще було б по другій. Але так як у мене були зауваження по цій статті, а також хотілося Ultrin'у показати як створюється проект в Квартус я вирішив нічого не переробляти.

Взагалі тема про ПЛІС стає популярною, а для мене особливо. Поки ще не прочитав усіх статей, але до сих пір не вирішу на якому виробнику зупинитися - Altera або Xilinx. У будь-якому випадку страшенно радий, що з'явилося це співтовариство і народ викладає статті на тему ПЛІС, а то починати тільки з зарубіжної літератури і даташітов якось сумно.

ЗИ. Паралельно намагаюся освоїти AVR. Нічо так))))))))))

ЗЗИ. Звернення до тих, хто знає і вміє: жахливо буду вдячний вам (напевно, не тільки я), якщо ви продовжите розповідати про цю цікаву тему з таким же ентузіазмом

У пострадянському просторі чомусь Альтеровская продукція більш популярна (ІМХО, можливо по-тому, що є офіційні центри Альтери), а ось за кордоном, особливо у японо-корейців і в європі дуже часто зустрічаюся з розробками під Xilinx. На мій погляд, російськомовних матеріалів під Альтера більше і вона простіше в освоєнні.

Ну збентежилася аж. Подивися ціни в терраелектроніке той-же.

А по сабжу: ось чому логіка хороша на відміну від контролера - це:

- Ну ясна річ, все распараллеліть (і це головне!). Вважай чогось, лей в UART, читай з SPI - все одночасно, аби пам'ять встигала (ну це, якщо вона взагалі потрібна).

- Мало якихось інтерфейсів? Додай хоч скільки, яких треба на одному камені.

Але є, звичайно, речі, для яких логіка, ІМХО, не дуже підходяща штука: наприклад підтримка FAT, стека TCP / IP ... і це все що я згадав :)

Так само, не слід займатися херней і намагатися запхати в логіку який-небудь проц, наприклад альтеровскій Nios II. Це безглуздо, краще взяти готовий, він все одно виграє по швидкості, а гемора буде сильно менше.

Ну якщо є невикористані ресурси, то вже краще помучитися і запхати Ніос, ніж, тулить зовнішній. А взагалі багато речей, які роблять на МКконроллерах / процесорі часто можна замінити не складним цифровим автоматом.

Для новачків пораджу ще непогану серію статей по Quartus I. Там є і компіляція, і призначення портів, і моделювання і ТаймКвест.

EasyEDA: безкоштовний Хмарний CAD