У схемотехніці блоків живлення дуже широке застосування знаходять стабілізатори з прохідним транзистором. У цій статті розглядаються причини використання таких схемотехнік, їх переваги, можливі схеми реалізації та принцип функціонування.

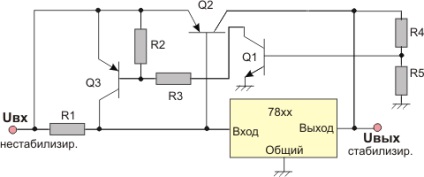

Трехвиводние інтегральні стабілізатори з фіксованою напругою випускаються на найрізноманітніші значення вихідних струмів, аж до 5 і більше Ампер. Як приклад, можна назвати 10-приміщення повинна бути захищена стабілізатор LM396. Разом з тим робота з такими великими струмами може виявитися небажаною, оскільки максимальна робоча температура для кристалів подібних стабілізаторів менше, ніж для кристалів потужних транзисторів, що призводить до необхідності використовувати громіздкі радіатори. Крім того, потужні інтегральні стабілізатори досить дороги. Альтернативне рішення полягає у використанні зовнішніх прохідних транзисторів, які можна додати до трьох-і четирехвиводним стабілізаторів, розрахованим для роботи з малими струмами (до 100 мА), наприклад, до стабілізаторів типу 7805, 7812 і т.д. Базова схема стабілізатора з прохідним транзистором показана на рис.1.

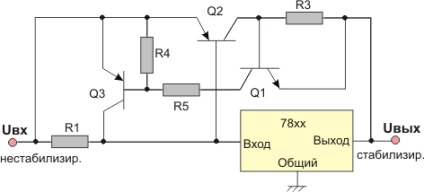

Рис.1 Базова схема стабілізатора з прохідним транзистором

Рис.1 Базова схема стабілізатора з прохідним транзистором

При токах менше 100 мА схема працює звичайним чином, тобто працює інтегральний стабілізатор. При великих токах навантаження, падіння напруги, що виникає на R1, призводить до відкривання транзистора Q1, і реальний струм через інтегральний стабілізатор обмежується величиною 100 мА. Інтегральний стабілізатор підтримує необхідне значення напруги на виході, шляхом регулювання вхідного струму. А так як база транзистора Q1 з'єднана з входом інтегрального стабілізатора, то, зміна вхідного струму мікросхеми призводить до зміни режиму роботи Q1. Якщо напруга на виході стабілізатора зростає, то стабілізатор зменшує свій вхідний струм і транзистор Q1 «прізакривается», зменшується струм його переходу колектор-емітер, що, в підсумку, веде до зменшення вихідної напруги, тобто здійснюється стабілізація. Якщо напруга на виході стабілізатора зменшується, то відбувається зворотний процес. Інтегральний стабілізатор в цьому випадку навіть не "знає", що навантаження споживає струм більше 100 мА. У цій схемі вхідний напруга повинна перевищувати вихідний на величину перепаду стабілізатора 78хх (2В) плюс напруга переходу база-емітер транзистора Q1.

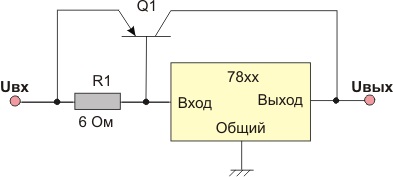

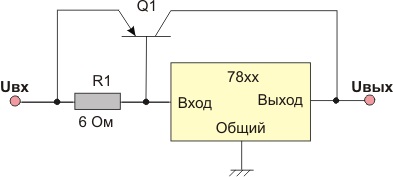

На практиці цю схему часто модифікують для того, щоб забезпечити обмеження струму транзистора Q1, який в іншому випадку може віддавати струм в h21Е разів перевищує максимальний внутрішній струм стабілізатора, тобто 20 А і більше! Цього достатньо для руйнування транзистора Q1 і підключеного навантаження. Найбільш часто використовуються методи обмеження струму, показані на рис.2 і рис.3.

Рис.2 Стабілізатор з прохідним транзистором і обмеженням струму прохідного транзистора

Транзистор Q2 в обох схемах є потужнострумових прохідним транзистором, а резистор між його базою і емітером обраний таким чином, щоб транзистор відкривався при струмі навантаження 100 мА.

На рис.2 транзистор Q1 реагує на струм навантаження за рахунок падіння напруги на R3 і обмежує запуск транзистора Q2 в тому випадку, якщо це падіння перевищує падіння напруги на діоді (напруга переходу база-емітер). Схема на рис.2 має два недоліки:

- вхідна напруга має тепер перевищувати стабілізовану вихідна напруга на величину падіння напруги на стабілізаторі плюс падіння на двох діодах (для струмів навантаження поблизу максимального струму);

- транзистор Q1 повинен витримувати великі струми (до максимального струму стабілізатора), так як через малого опору резистора в базі Q1 важко реалізувати обмежує схему зі зворотним нахилом характеристики.

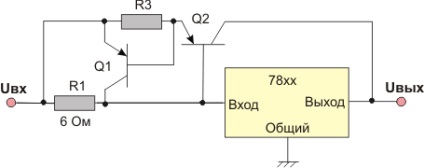

Рис.3 Стабілізатор з прохідним транзистором і обмеженням струму прохідного транзистора

У схемі на рис.3 ці недоліки усунуті за рахунок деякого ускладнення. У сільноточних стабілізаторах для зменшення потужності, що розсіюється до прийнятного рівня, важливо домогтися малого перепаду напруги. Щоб отримати в цій схемі характеристику зі зворотним нахилом, можна просто підключити базу Q1 до делителю між колектором і "землею", а не до колектора Q2, як це і зроблено в схемі на рис.4.