На основі статті Торстена Гёцельманна, інженера компанії Keysight Technologies (Thorsten Götzelmann ThorstenG)

З Вікіпедії:

PCI Express. або PCIe. або PCI-E (також відома як 3GIO for 3rd Generation I / O) - комп'ютерна шина (хоча на фізичному рівні шиною не є, будучи з'єднанням типу «точка-точка»), яка використовує програмну модель шини PCI і високопродуктивний фізичний протокол, заснований на послідовної передачі даних.

Специфікації PCI Express

базові специфікації

специфікації CEM

Найпоширенішою моделлю застосування PCI Express є, ймовірно, слот розширення PCI Express, певний в електромеханічних характеристиках плати PCI Express (CEM). В процесі тестування приймачів треба враховувати два різних типи пристроїв: плати розширення і материнські (системні) плати. CEM використовує тільки синхронний режим роботи і є єдиною екосистемою PCI Express, що пропонує обов'язкову програму сертифікації відповідності стандарту, включаючи тести фізичного рівня. Всі пристрої, що входять до переліку інтеграторів PCI-SIG, повинні проходити перевірку відповідності в одній з випробувальних лабораторій PCI-SIG. Необхідні тести відповідності фізичного рівня визначені в специфікації тестування архітектури фізичного рівня PCI Express (CTS). Тести CTS розроблені так, щоб їх можна було виконувати в лабораторних умовах.

В результаті тестування приймачів згідно CTS може виявитися не настільки строгим і менш складним, ніж тестування згідно з базовими специфікаціям.

Специфікації тестування фізичного рівня (M-PHY)

M-PCIe замінює фізичний рівень PCI Express фізичним рівнем, визначеним для M-PHY. Отже, тести приймача повинні виконуватися відповідно до специфікації M-PHY, а не специфікацією PCI Express. M-PHY - це фізичний рівень, певний Альянсом MIPI®.

Вимоги до тестування приймачів PCI Express

Вимоги до тестування і методи калібрування не однакові для різних швидкостей передачі даних. У специфікації PCIe 3.0 опорна точка переноситься всередину чіпа, і структура спотвореного випробувального сигналу стає складніше. Крім того, використовувана для тестування приймачів методологія, що описує міжсимвольні перешкоди в каналі, відрізняється для швидкостей 2,5 / 5 ГТ / с і 8/16 ГТ / с.

Також вимоги до тестування визначають сумісність. Тобто, пристрій, здатний працювати на більш високих швидкостях, має бути сумісним і з меншими швидкостями передачі даних.

PCI Express 2,5 ГТ / с

Специфікації приймача визначені на висновках приймача. Специфікації ідентичні для різних схем тактирования і для синхронного і асинхронного режимів роботи. Визначено тільки проста маска приймача. Оскільки специфікації випадкового джиттера (RJ) відсутні, зазвичай використовуються значення RJ, певні для швидкості 5 ГТ / с. Тестування з базових специфікаціям не вимагає внесення предискаженій, а ось тестування відповідно до CEM - вимагає.

Фактори, що визначають найгірші умови:

- Міжсимвольні перешкоди (ISI) через зовнішній канал. Міжсимвольні перешкоди повинні бути основним компонентом детермінованого джиттера (DJ). Для тестів CEM потрібна базова плата для перевірки відповідності PCI-SIG (CBB) і плата навантаження для перевірки відповідності (CLB). Плату CBB для gen1 і gen2 слід настроїти так, щоб її можна було використовувати для тестування приймачів

- Випадковий джиттер (RJ)

- Для забезпечення необхідного закриття очі міжсимвольні перешкоди доповнюються синусоїдальним джиттером (SJ)

- Синфазна синусоїдальна перешкода (CM-SI), тільки для базових специфікацій

PCI Express 5 ГТ / с

Специфікації приймача також визначені на висновках приймача. Базові специфікації визначають різні параметри для приймачів, які використовують CC або DC. Специфікації CEM не застосовуються CM-SI, але додають другий високочастотний тон джиттера. Для сценаріїв застосування CC визначений залишковий SSC (rSSC); rSSC є трикутною фазову модуляцію, яка застосовується тільки до спотвореного випробувального сигналу, але не до опорної тактовій частоті. Він визначає собою найгірші умови, в яких може опинитися приймач між SSC опорної тактової частоти і SSC вхідного сигналу даних.

Фактори, що визначають найгірші умови:

- Міжсимвольні перешкоди через зовнішній канал. Міжсимвольні перешкоди повинні бути основним компонентом регулярного джиттера. Для тестів CEM потрібна базова плата для перевірки відповідності PCI-SIG (CBB) і плата навантаження для перевірки відповідності (CLB). Плату CBB для gen1 і gen2 слід змінити так, щоб її можна було використовувати для тестування приймачів.

- Відфільтрований по спектру випадковий джиттер (sRJ) з більшою амплітудою для частотного спектра до 1,5 МГц і меншою амплітудою для частотного спектра від 1,5 до 100 МГц

- Для забезпечення необхідного закриття очі міжсимвольні перешкоди доповнюються синусоїдальним джиттером (SJ)

- SSC:

- rSSC використовується для реалізацій на основі CC, крім тестування систем на основі CEM, оскільки SSC визначається тактовою частотою системи

- SSC використовується для реалізацій на основі DC

- CM-SI, тільки для базових специфікацій

- Вторинний високочастотний тон SJ тільки для специфікацій CEM

PCI Express 8 ГТ / с

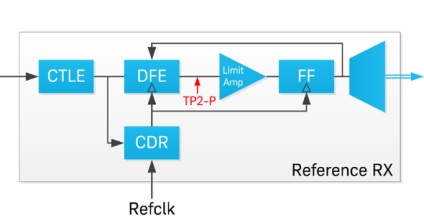

Мал. 1. Опорна точка TP2-P, певна в специфікаціях приймача PCIe 8 ГТ / с

Підвищена швидкість передачі практично по тому ж каналу робить необхідної корекцію приймача, тому тестування приймача набуває великої важливості. Специфікації приймача описуються більш детально і визначаються всередині приймача після коректорів (CTLE і DFE). Ця опорна точка називається TP2-P. Внаслідок зсуву визначення опорної точки, для калібрування спотвореного випробувального сигналу доводиться застосовувати вбудовування поведінкового пакета приймача, а також імітацію коригувальних ланцюгів і відновлення тактової частоти.

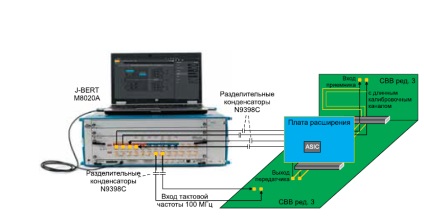

Мал. 2. Приклад схеми для тестування приймача плат розширення PCIe 8 ГТ / с

Фактори, що визначають найгірші умови:

- Міжсимвольні перешкоди через зовнішній канал. Для тестів CEM потрібна базова плата для перевірки відповідності PCI-SIG (CBB), перехідник і плата навантаження для перевірки відповідності (CLB) для gen3 для довгого каналу і CBB gen2 для короткого каналу

- Випадковий джиттер з фільтром верхніх частот 10 МГц

- Синусоїдальний джиттер, різні маски допуску джиттера для CC і SRNS / SRIS

- SSC, тільки для SRIS:

- Трикутний розподіл в нижню сторону на 33 кГц для тестування з граничним напруженням

- Синусоїдальна розподіл в нижню сторону на 33 кГц для тестування з граничним джиттером

- DM-SI

- CM-SI, тільки для базових специфікацій

Після поліпшення фізичних можливостей приймачів PCIe, в процедуру навчання каналу була додана оптимізація корекції передавача, яка враховує характеристики поточного каналу, передавача і приймача.

PCI Express 16 ГТ / с

PCI Express 4-го покоління буде підтримувати швидкість 16 ГТ / с. Специфікації 4.0 ще не випущені, і в даний час робота над ними триває. Проте робочі групи PCI-SIG, що працюють над версією 4.0 і специфікаціями приймача 16 ГТ / с, швидше за все, будуть слідувати методам калібрування приймачів 8 ГТ / с з поліпшеннями, спрямованими на підвищення сумісності між різними схемами випробувань. Налаштування ширини і висоти вічка за випадковим джиттеру і DM-SI в процесі калібрування приймача PCIe 8 ГТ / с в поєднанні з допуском на смугу каналу ± 2 дБ, мабуть, буде проблематичною. Схеми з меншими втратами можуть зажадати значно більшого випадкового джиттера для закриття очі до заданих значень в порівнянні зі схемами з високими втратами. Але більшість приймачів краще справляється з міжсимвольні перешкодами, викликаними втратами в каналі, ніж з випадковим джиттером, і в результаті дві схеми вимірювання можуть створити несумісні умови випробувань. Для виправлення цієї ситуації стандарт посилює допуски для випробувальних каналів, вимагаючи деякого роду настройки міжсимвольних перешкод, наприклад, шляхом вибору канальних плат з різним значенням міжсимвольних перешкод.

Попередні фактори, що визначають найгірші умови:

- Міжсимвольні перешкоди через настроюється або обираний зовнішній канал. Тестування CEM, ймовірно, зажадає застосування тестової оснащення, що розробляється і поставляється PCI-SIG

- Випадковий джиттер з фільтром верхніх частот 10 МГц

- Синусоїдальний джиттер, різні маски допуску джиттера для CC і SRNS / SRIS

- SSC, тільки для SRIS:

- Трикутний розподіл в нижню сторону на 33 кГц для тестування з граничним напруженням

- Синусоїдальна розподіл в нижню сторону на 33 кГц для тестування з граничним джиттером

- DM-SI

- CM-SI, тільки для базових специфікацій

Тестування корекції каналу

Тести корекції каналу можуть відрізнятися для приймачів і передавачів. Тести приймачів мало відрізняються від класичних тестів приймачів за винятком того, що приймач тестованого пристрою «домовляється» з передавачем BERT про частотної корекції та налаштування попереднього підйому характеристики, які використовуються для тестування даного приймача. Калібрування спотвореного випробувального сигналу ідентична класичним тесту приймачів 8 ГТ / с.

Тестування корекції каналу передавача фокусується на двох факторах:

- Фактична форма сигналу, заснована на запитах партнера по каналу. Це включає зміни фактичної форми сигналу, а також гарантує, що сигнал відповідає вимогам цільових специфікацій

- Час реакції на запити зміни з боку партнера по каналу. Воно складається з часу логічної відповіді і часу фізичного відповіді. Часом логічної відповіді називається час між запитом на зміну і відправкою підтвердження партнеру, тоді як часом фізичного відповіді називається час від запиту на зміну до реального зміни форми сигналу.

висновок

З кожною новою редакцією стандарт PCI Express розширює межі можливостей передачі даних по каналах, реалізованим на платах з склотекстоліти FR4, і тому приймачі постійно ускладнюються. В результаті доводиться застосовувати контрольно-вимірювальне обладнання з великим набором можливостей і більш складні схеми тестування. Виробники контрольно-вимірювального обладнання змушені реагувати на ці нові вимоги. Хорошим прикладом є розвиток систем BERT компанії Keysight Technologies. Наприклад, система J-BERT M8020A BERT наочно демонструє інтеграцію класичних компонентів BERT в одному приладі, що дозволяє отримати нові можливості, такі як LTSSM, націлені на подолання нових труднощів тестування.

PCIe і PCI Express є зареєстрованими товарними знаками PCI-SIG®.

MIPI є зареєстрованим в США та інших країнах товарним знаком MIPI, Inc.