Останнім часом відомий китайський сайт пропонує купити радіоаматорам різного роду налагоджувальні плати на ПЛІС. але на жаль, доступного для непідготовленого розуму (ну або такого, яке б мені сподобалося) опису російською (як же ЦЕ працює?) на просторах інтернету я не знайшов. Згодом, звичайно, розуміння прийшло, але також прийшло і бажання написати якусь вступну статтю з красивими картинками, які б наочно пояснювали суть ПЛІС. Почнемо.

ПЛІС - Програмована Логічна Інтегральна Схема. ВАЖЛИВО! Існує два типи БІС (Велика Інтегральна Схема), які у нас в СНД потрапляють під визначення ПЛІС, але тим не менше принцип роботи цих БІС відрізняється, що створює певний дисонанс з реальним станом речей. У той же час на заході у кожної з цих БІС є цілком свою власну назву, чітко ставить всі крапки над i, а саме: CPLD-мікросхема - це ПЛІС, прошивка (конфігурація) якої ЗАВЖДИ зберігається в самій мікросхемі і при виключенні живлення НІКОЛИ не стирається. Здається цілком собі логічним, що прошивка само-собою повинна зберігається в мікросхемі, і загострювати увагу на цьому не слід, але перейдемо до наступної БІС. FPGA-мікросхема - це теж ПЛІС, але її конфігурація зберігається на зовнішньому незалежному джерелі пам'яті (наприклад всякого роду flash). Як це працює? Дуже просто, при кожному включенні, FPGA прошиває саму себе конфігурацією, яку бере з пам'яті, а при виключенні стирається.

Хочеться відзначити, що процес написання конфігурації на CPLD і на FPGA нічим не відрізняється: все пишеться на мові опису апаратури VHDL або Verilog. Потім відбувається синтез і імплементація (компілятор спочатку намагається зрозуміти, що ви написали, а потім намагається розмістити всі структури, регістри і з'єднання в ПЛІС, на основі написаного), і на останньому етапі генерується .bit - файл, який зашивається программатором по JTAG-інтерфейсу в пристрій.

Якщо з CPLD ще якось звичніше працювати ( "Ну як в мікроконтролері!" - скажете Ви), то FPGA, з усіма її незрозумілими зовнішніми джерелами пам'яті, здаються якимось безглуздим звіром, тому все нижче написане буде присвячено FPGA (але прийоми програмування справедливі і для CPLD), щоб внести якусь ясність в це питання. Всі приклади коду будуть виконуватися на мові VHDL.

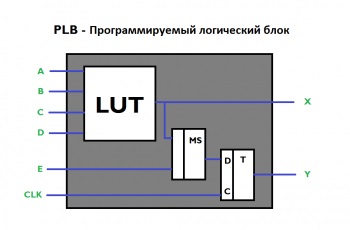

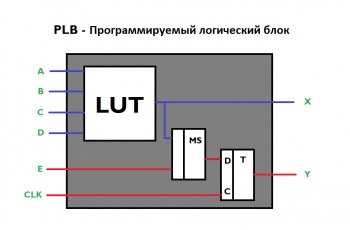

Розглянемо найменшу складову FPGA, яка називається PLB - Програмований Логічний Блок.

PLB складається з LUT-таблиці відповідності, мультиплексора і D-тригера. Розглянемо для початку LUT. По-суті, LUT - це статичне ОЗУ (ОЗУ - оперативне запам'ятовуючий пристрій. Є енергозалежною пам'яттю, тобто при відключенні живлення дані стираються. (Включив. Записав. Вимкнув. Включив знову, а всі записані дані стерті). Володіє високими показниками швидкості.), в якому зберігаються вихідні значення X, утворені значеннями A, B, C, D.

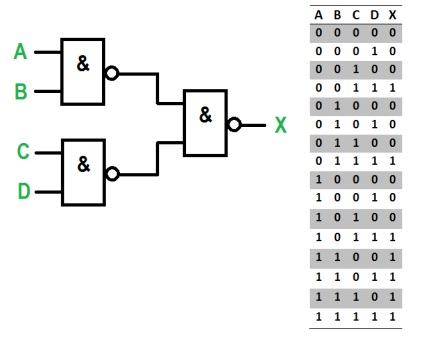

Припустимо нам потрібно реалізувати на ПЛІС схему представлену на малюнку нижче, з відповідною таблицею істинності:

Сигнали A, В, С, D подаються на вхід LUT, далі виходячи з таблиці істинності, яка зберігається в LUT, моментально формується сигнал X. Все дуже просто. У коді це виглядає так:

X <= (A nand B) nand (C nand D);

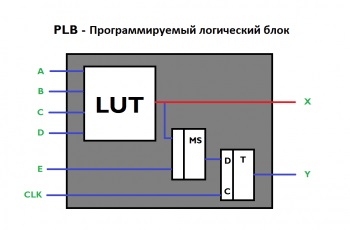

На малюнку нижче червоною лінією показано, як формується вихідний сигнал на апаратному рівні:

Але що, якщо нам потрібно синхронізувати сигнал по тактовій частоті? Тоді, в процесі написання конфігурації, нам потрібно вказати, що вихідний сигнал буде встановлюватися або по фронту (rising_edge (clk)) або по зрізу (falling_edge (clk)) тактового сигналу CLK, і компілятор буде брати вихідний сигнал НЕ c виходу X, а з виходу Y. мовою VHDL це виглядає так:

if (rising_edge (clk)) then

Y <= (A nand B) nand (C nand D);

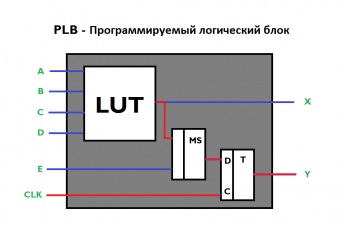

На апаратному рівні це відбувається так: сигнал з LUT йде на Т-тригер, який встановлює значення виходу Y по CLK.

Що робити якщо потрібно затримати вхідний сигнал на один такт? Тоді в конфігурації ми присвоюємо сигнал, який потрібно затримати, новому сигналу в процесі синхронізований по CLK:

if (rising_edge (clk)) then

Апаратно це відбувається так:

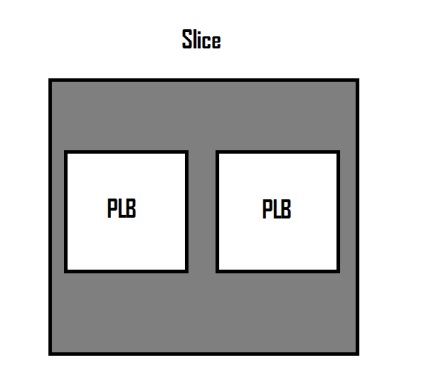

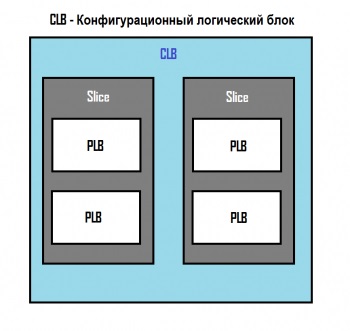

Нагадаю, все вище розглянуте відбувається в рамках ОДНІЄЇ найменшими складової FPGA, а саме PLB. Але всередині FPGA десятки тисяч таких PLB (а може і сотні, технології вони такі: не стоять на місці), які можуть з'єднуватися між собою. Для простоти організації зв'язків між ними, в FPGA застосовується якийсь модульний принцип: мале становить велику: дві PLB утворюють один SLICE.

На завершення хотілося б розповісти чому варто придивитися до ПЛІС, і зокрема до FPGA-мікросхем. По-перше це необмежене поле для творчості: потрібен екзотичний 13-бітний таймер / лічильник? - отримай. Потрібно 15 UART? - легко. Передати дані зі швидкістю 6 Гбіт / с? - не питання. І якщо переваги ПЛІС очевидні, то перейдемо до того яка з них краще: CPLD або FPGA? Хочеться відзначити, що власне тут все залежить від застосування. Якщо проект не великий, але вимагає специфічної периферії, то це CPLD. А якщо потрібна гнучкість і дуже великі швидкості, то це FPGA. Ніщо не заважає вам зробити так, щоб в якийсь момент часу FPGA працювала спочатку по-одній прошивці, потім по-другої, третьої, п'ятої, десятої (властивість реконфігурованих), адже на відміну від інших мікросхем, ресурс запис / стирання у FPGA прагнути до нескінченності (коли останній раз ви міняли оперативну пам'ять в своєму ПК через те, що виробили її ресурс на запис / стирання? Ось і я про це. Власне на цьому все, спасибі за увагу

Тут я по вашому посиланню, побачив мінімальну системну плату зі встановленою на неї ALTERA FPGA CycloneII EP2C5T144. Так ось, про що це я, для використання цієї плати мені доведеться підключити до неї зовнішню флеш мікросхему пам'яті? Або, прошивку необхідно буде завантажувати байтбластером при кожному включенні плати, і вона буде працювати до відключення живлення без зовнішньої пам'яті?

На самій отладочной платі вже є мікросхема пам'яті, де буде зберігатися прошивка, так що особисто Вам припаювати пам'ять не доведеться. Що стосується процесу прошивки, то коли Ви будете прошивати, середа запропонує Вам вибрати куди завантажити прошивку: в FPGA мікросхему або в FLASH мікросхему. Якщо Ви завантажте в FPGA, то так, при відключенні харчування прошивка зітреться, якщо в FLASH, то при відключенні харчування прошивка залишиться під FLASH, і вже при повторному включенні FPGA сама завантажить в себе прошивку з FLASH, без допомоги ByteBlaster'a.

Для відповіді треба знати в яку суму для покупки ви маєте в своєму розпорядженні.

Але в загальному випадку для зовсім початківців можу порекомендувати відразу брати нормальну FPGA, а не CPLD і більш-менш сучасного покоління, наприклад

І для початку краще від Альтери, у них ПО більш адекватне і наочне.