До здійснення компіляції необхідно також вибрати сімейство ПЛІС для реалізації спроектованого пристрою (якщо Ви не зробили цього раніше при створенні проекту): Assignments -> Device ..., вибір необхідного сімейства проводиться в поле Family.

Якщо перед запуском компілятора не опинився відкритим потрібний проект, то його необхідно відкрити. Для цього потрібно або відкрити який-небудь файл даного проекту і рухатися по меню File -> Project -> Set Project to Current File.

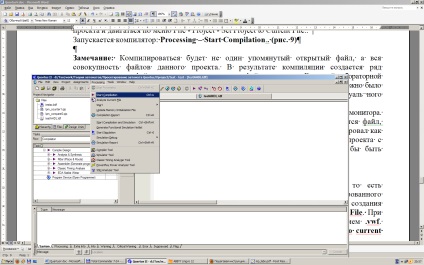

Компіляція запускається командою: Processing -> Start Compilation. (Рис.9)

Мал. 9Запуск компіляції

Компілюватиметься буде не один згаданий відкритий файл, а вся сукупність файлів даного проекту. В результаті створюється ряд допоміжних файлів, які не належать до файлів проекту.

У проекті обов'язково повинен бути файл з ім'ям, яке Ви вказали в якості Top-Level design entity (в нашому прикладі - test). Наприклад, файл схеми або AHDL-опису. Воно буде являти собою верхній модуль вашого проекту. В іншому випадку компілятор видасть помилку: Top-Leveldesignentity "file_name" isundefined.

4 Перевірка проекту

Наступним етапом після компіляції є верифікація проекту, тобто моделювання та перевірка правильності функціонування спроектованого пристрою.

Після компіляції потрібно створити спеціальний список netlist для функціональної симуляції. Вибираємо пункт менюProcessing-> GenerateFunctionalSimulationNetlist. Симуляція буває тимчасова і функціональна. Функціональна симуляція дозволяє перевірити саме логіку роботи. З її допомогою ми можемо переконатися, що проект може і повинен працювати так, як задумано. Перш за все, потрібно робити саме функціональну симуляцію. Тимчасова симуляція дозволяє побачити сигнали з урахуванням всіх виникаючих затримок сигналу між елементами, входами і виходами. Тимчасову симуляцію роблять в останню чергу, вже після функціональної симуляції, щоб переконатися, що схема може працювати на заданій частоті. Для невеликих проектів, цілком достатньо виконати тільки функціональну симуляцію.

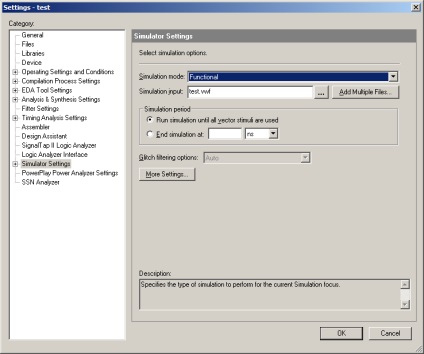

Для завдання типу симуляції використовується пункт меню Assignment -> Settings. У діалоговому вікні Settings вибирається розділ Simulator Settings. Тут потрібно задати тип симуляції -Functional. функціональна. Задаємо ім'я вхідного файлу симуляції * .vwf. натискаємо OK. Тепер все готово для симуляції (рис.10).

Мал. 10Установкі симуляції

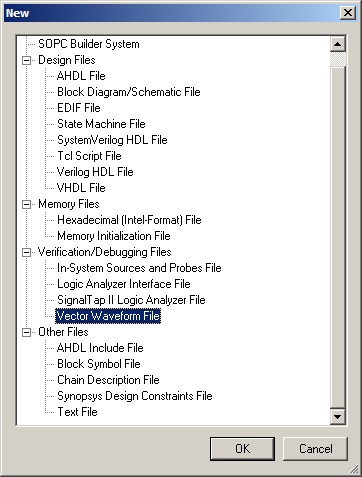

Зазначені установки можна зробити і після створення файлу діаграм. В цьому випадку для верифікації проекту необхідно рухатися по меню File -> New -> Verification / DbuggingFiles-> Vector Waveform File. (Рис. 11)

Ріс.11Созданіе файлу тимчасових діаграм