FPGA - це скорочення від англійського словосполучення Field Programmable Gate Array.

ПЛІС - це скорочення від словосполучення «Програмована Логічна Інтегральна Схема». Слово ПЛІС зустрічається в російськомовних документациях і описах замість слова FPGA. Далі по тексту в основному буде використовуватися цей термін - ПЛІС.

ПЛІС і FPGA - це абревіатури, що позначають один і той же клас електронних компонентів, мікросхем. Це мікросхеми, що застосовуються для створення власної структури цифрових інтегральних схем.

Логіка роботи ПЛІС визначається не на фабриці виробником мікросхеми, а шляхом додаткового програмування (в польових умовах, field-programmable) за допомогою спеціальних засобів: программаторов і програмного забезпечення.

Мікросхеми ПЛІС - це не мікропроцесори, в яких призначена для користувача програма виконується послідовно, команда за командою. У ПЛІС реалізується саме електронна схема, що складається з логіки і тригерів.

Проект для ПЛІС може бути розроблений, наприклад, у вигляді принципової схеми. Ще існують спеціальні мови опису апаратури типу Verilog або VHDL.

У будь-якому випадку, і графічне і текстове опис проекту реалізує цифрову електронну схему, яка в кінцевому рахунку буде «вбудована» в ПЛІС.

Зазвичай, сама мікросхема ПЛІС складається з:

- конфігуруються логічних блоків, що реалізують необхідну логічну функцію;

- програмованих електронних зв'язків між конфігуруються логічними блоками;

- програмованих блоків введення / виводу, що забезпечують зв'язок зовнішнього виведення мікросхеми з внутрішньою логікою.

Строго кажучи це не повний список. В сучасних ПЛІС часто бувають вбудовані додатково блоки пам'яті, блоки DSP або умножители, PLL і інші компоненти. Тут, в цій статті я їх розглядати не буду.

Розробник проекту для ПЛІС зазвичай абстрагується від внутрішньої будови конкретної мікросхеми. Він просто описує бажану логіку роботи «своєї» будещее мікросхеми у вигляді схеми або тексту на Verilog / VHDL. Компілятор, знаючи внутрішній устрій ПЛІС сам намагається розмістити необхідну схему за наявними конфігурованим логічним блокам і намагається поєднати ці блоки за допомогою наявних програмованих електронних зв'язків. У загальному випадку розміщення і трасування зв'язків між логічними блоками в ПЛІС залишається за компілятором.

Класифікація ПЛІС за типом зберігання конфігурації.

SRAM-Based.

Це одна з найпоширеніших різновидів ПЛІС. Конфігурація ПЛІС зберігається осередках статичної пам'яті, виготовленої за стандартною технологією CMOS.

Гідність цієї технології - можливість багаторазового перепрограмування ПЛІС. Недоліки - не найвища швидкодія, після включення живлення прошивку потрібно знову завантажувати. Значить на платі повинен ще стояти завантажувач, спеціальна мікросхема FLASH або мікроконтролер - все це здорожує кінцевий виріб.

Flash-based.

У таких мікросхемах зберігання конфігурації відбувається у внутрішній FLASH пам'яті або пам'яті типу EEPROM. Такі ПЛІС краще тим, що при виключенні живлення прошивка не пропадає. Після подачі живлення мікросхема знову готова до роботи. Однак, у цього типу ПЛІС є і свої недоліки. Реалізація FLASH пам'яті всередині CMOS мікросхеми - це не дуже просто. Потрібно поєднати два різних техпроцесу для виробництва таких мікросхем. Значить вони виходять дорожче. Крім того, такі мікросхеми, як правило, мають обмежену кількість циклів перезапису конфігурації.

Antifuse.

Спеціальна технологія по якій виконуються одноразово програмовані ПЛІС. Програмування такої ПЛІС полягає в расплавлении в потрібних місцях чіпа спеціальних перемичок для утворення потрібної схеми.

Недолік - власне програмувати / прошивати чіп можна тільки один раз. Після цього виправити вже нічого не можна. Сам процес прошивки досить не швидкий. Зате є маса переваг у таких ПЛІС: вони досить швидкі (можуть працювати на високих частотах), менше схильні до збоїв при радіації - все через те, що конфігурація виходить у вигляді перемичок, а не у вигляді додаткової логіки, як у SRAM-based .

Конфігуровані логічні блоки.

У документації компанії Альтера зустрічається вираз Logic Array Block (LAB) - масив логіки. У компанії Xilinx в мікросхемах ПЛІС є приблизно такі ж блоки - Configurable Logic Block (CLB). Конфігурується логічний блок - це базовий елемент в ПЛІС, в ньому може бути виконана якась проста логічна функція або реалізовано зберігання результату обчислення в регістрах (тригерах).

Складність і структура конфигурируемого логічного блоку (CLB) визначається виробником.

Теоретично, конфігурується логічний блок може бути, наприклад, дуже простим, просто як окремий транзистор. Або він може бути дуже складним, як цілий процесор. Це крайні точки реалізації.

У першому випадку буде потрібно величезна кількість програмованих зв'язків, щоб потім з окремих транзисторів зібрати необхідну схему. У другому випадку зв'язків може потрібно і не так багато, але втрачається гнучкість проектування користувальницької схеми.

Саме тому конфігурується блок зазвичай представляє з себе щось середнє: він зазвичай досить складний, щоб можна було б зашити туди деяку функцію, а й досить малий, щоб розмістити безліч таких блоків всередині ПЛІС і щоб була можливість зв'язати їх в єдину схему.

Таким чином, вибір структури конфигурируемого логічного блоку виробником ПЛІС - це завжди пошук компромісу по площі кристала, по швидкодії, енергоспоживання і так далі.

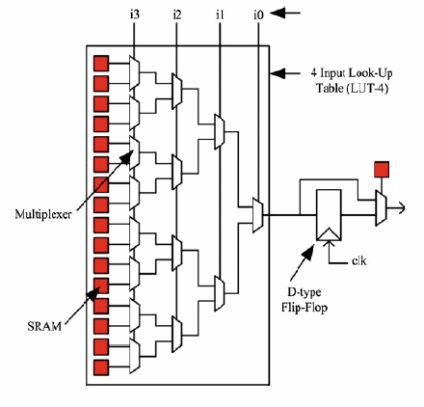

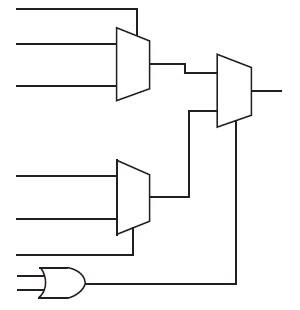

Конфігурується логічний блок може складатися з одного або декількох базових логічних елементів. В англомовній літературі це Basic Logic Element (BLE) або просто Logic Element (LE). У ПЛІС зазвичай використовуються так звані LUT-based базові логічні елементи. Щось на зразок цього:

Мал. 1. Приклад традиційного базового логічного елемента.

LUT - це Look-Up Table, таблиця перетворення. Наприклад, на Рис.1 показаний четирехбітних LUT в складі базового логічного блоку. Тут четирехбітних числу на вході логічного функції ставиться у відповідність однобітний результат. Червоні квадратики на Рис. 1 позначають програмований елемент, регістр - це та пам'ять, де зберігається прошивка для ПЛІС. Видно, що для конфігурації 4-х бітного LUT потрібно 16 конфігураційних регістра. Вміст цих регістрів визначають логічну функцію, реалізовану всередині базового логічного елемента.

Ще один конфігураційний регістр (на Рис. 1 це одиночний червоний квадратик праворуч) визначає чи потрібно на вихід базового логічного елемента видавати прямо значення з LUT або потрібно видати зафіксоване в D-тригері значення з LUT. Фіксація і зберігання даних в цифрових схемах потрібна практично в будь-якому проекті.

Розглядаючи Рис. 1 як приклад традиційного базового логічного елемента розумієш яка надмірність закладена всередину сучасного кристала ПЛІС (SRAM-based). Адже справді, конфігураційні регістри (червоні квадратики) прямо не доступні для використання в цифровому проекті. Вони тільки служать для формування користувальницької функції. Для одного D-тригера в призначеному для користувача проекті потрібно більше 16 (іноді багато більше) тригерів для зберігання конфігурації ПЛІС.

Насправді базовий логічний елемент в різних ПЛІС виявляється набагато складніше, ніж показано на Рис. 1. Нижче є деякі приклади з документації на різні типи ПЛІС.

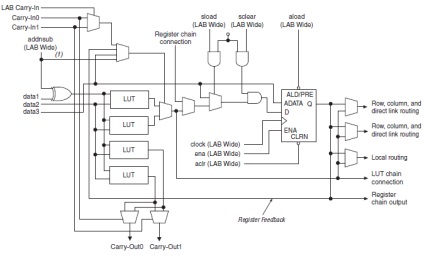

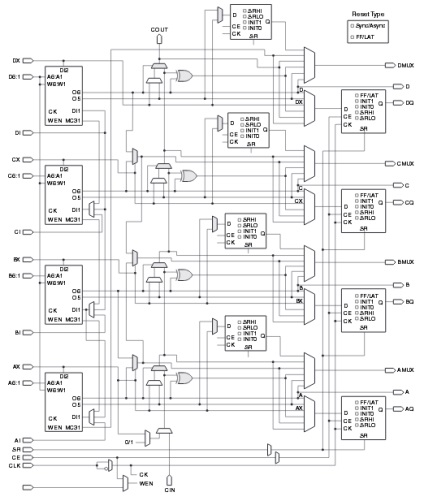

Мал. 2. Базовий логічний елемент CPLD MAX II компанії Альтера.

Тут добре видно LUT і D-Тригер зберігання результату. Нижче, на Рис. 3 представлений базовий елемент Cyclone III.

Мал. 3. Базовий логічний елемент FPGA Cyclone III компанії Альтера.

У мікросхемах Альтери в одному LAB може міститися 10-16 LE.

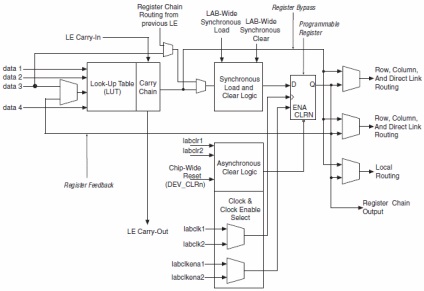

У мікросхемах компанії Xilinx Virtex-6 базовий логічний елемент - це так званий Slice. В одному CLB всього два Slice. Зате один Slice - це досить складний пристрій:

Мал. 4. Базовий елемент Xilinx Virtex-6 Slice.

В одному CLB Virtex-6 є 8 LUT і 16 D-Тригерів і ще дещо плюс до цього. Ось так все складно.

Інша крайність - мікросхеми FPGA компанії Microsemi (колишня Actel).

Наприклад, в мікросхемах серії 40MX базовий логічний елемент виглядає ось так:

Мал. 5. Logic Module of Microsemi 40MX serie.

Вісім входів і один вихід.

Тут немає ні Look-Up Table, ні навіть D-Трігера. Тригера, як і решта логіка, формуються де потрібно з ось таких крихітних цеглинок - Logic Module.

Чому у різних компаній вийшла така велика різниця в реалізації базового логічного елемента? Мабуть в мікросхемах Microsemi зв'язок між базовими блоками обходиться набагато дешевше: серія 40MX є одноразово програмованої. У ній міжблочні зв'язку «проплавляются» між з'єднують доріжками і пізніше не можуть бути змінені. Немає ніяких регістрів для тимчасового зберігання прошивки. Тут немає програмованих перемикачів, мультиплексорів, як в FPGA інших типів. Ну мікросхеми компанії Microsemi - це кілька особливий випадок. Це технологія називається antifuse - для виробництва таких мікросхем використовується модифікований техпроцес CMOS з додатковими шарами для організації міжблочних зв'язків.

Програмовані зв'язки між логічними блоками.

Щоб в ПЛІС заробила потрібна нам цифрова схема мало того, що потрібно конфігурувати наявні логічні блоки особливим чином, ще потрібно створити, запрограмувати зв'язку між логічними блоками.

Для цього в ПЛІС є спеціальні конфігуруються комутатори.

В англомовній документації зустрічаються такі терміни: FPGA Routing Architecture і Programmable Routing Interconnect. Це все про це, про програмованих зв'язках між логічними блоками.

Відомо дві основні методики побудови ПЛІС за типом архітектури зв'язків: острівна і ієрархічна.

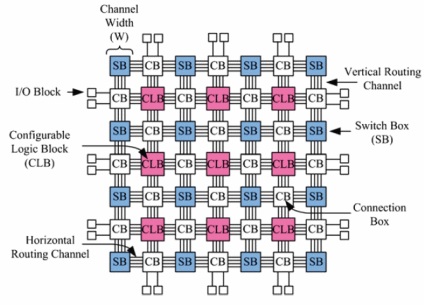

Мал. 6. Острівна ПЛІС.

Острівна ПЛІС називається так тому, що конфігуруються блоки усі рівні між собою і знаходяться, як острова в океані, між вузлами комутації та лініями зв'язку.

Тут, на Рис. 6 позначаються CB - Connection Box і SB - Switch Box. По суті це програмовані мультиплексори, підключають той чи інший CLB до іншого CLB через ланцюжки проводів в ПЛІС.

Це island-style FPGA або mesh-based FPGA. Типовий приклад таких мікросхем - це серії Altera Cyclone і Stratix.

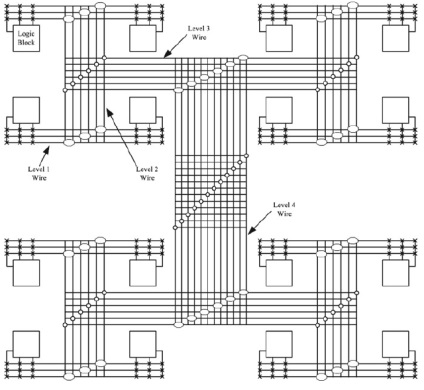

Другий відомий тип ПЛІС - це ієрархічні ПЛІС. Тут йде розрахунок на те, що в схемі завжди є ділянки які взаємодіють один з одним більш тісно, ніж з віддаленими модулями проекту.

Мал. 7. Ієрархічна ПЛІС.

Тут прилеглі CLB з'єднати досить просто, потрібно не багато комутаторів і виходять зв'язку працюють швидко. Ось якщо потрібен більший блок обчислювачів, то сигнал повинен вийти на більш високий рівень ієрархії і потім зайти всередину в сусідню «кімнату».

Не можна сказати, що це істотно гірше, ніж island-style. Просто кожен метод має свої плюси і мінуси.

Типові представники ієрархічних ПЛІС - це мікросхеми компанії Альтера серії Flex10K, APEX.

Програмне забезпечення для проектування ПЛІС.

Програмне забезпечення для проектування ПЛІС, а саме компілятор (синтезатор логіки і Фіттер і асемблер) - це, можливо, найскладніша частина всієї ПЛІС технології.

Компілятор повинен проаналізувати призначений для користувача проект (схеми і текстові описи на Verilog HDL або VHDL) і згенерувати нетліст (netlist) - список всіх елементів схеми і зв'язки між ними. Netlist повинен бути оптимізований - логічні функції потрібно мінімізувати, можливі дубльовані регістри потрібно видалити.

Потім компілятор повинен вмістити всю логіку з netlist в наявну архітектуру ПЛІС. Це робить Фіттер (fitter). Він розміщує логічні елементи і виконує трасування зв'язків між ними (процес place and route). Складність полягає в тому, що один і той же проект може бути розміщений в ПЛІС різними способами і цих способів мільйони. Деякий розміщення і трасування виявляються краще, інші гірше. Головний критерій якості отриманої системи - максимальна частота, на якій зможе працювати проект при даному розміщенні елементів і при даній трасування зв'язків. Тут впливає довжина зв'язків між логічними блоками і кількість програмованих комутаторів між ними.

Компілятор, знаючи архітектуру ПЛІС за результатами роботи додатково видає звіт про час проходження сигналів від регістру до регістру. Ця інформація часто буває корисною для розробника високопродуктивних систем. Розробник для ПЛІС має можливість давати деякі поради компілятору де, в якому місці кристала краще розмістити той чи інший модуль проекту.

Вибираючи для свого проекту, для своєї плати конкретну мікросхеми ПЛІС розробник в деякій мірі потрапляє в залежність від виробника цієї ПЛІС, так як повинен в роботі користуватися програмним забезпеченням від цього ж виробника.

Програмне забезпечення компанії Альтера: Quartus II.

ПО Xilinx для проектування для ПЛІС: ISE Suite, Vivaldo Design Suite.

ПО компанії Microsemi: Libero IDE, Libero SoC.

Можливо, програмне забезпечення, компілятори для ПЛІС - це найважливіша складова інтелектуальної власності компаній виробників ПЛІС.