Організація прямого доступу до пам'яті

Контролер прямого доступу до пам'яті КР580ІК57 (КР580ВТ57)

Послідовність програмування контролера

Організація прямого доступу до пам'яті

Одним із способів обміну даними з ВУ є обмін в режимі прямого доступу до пам'яті (ПДП). В цьому режимі обмін даними між ВУ і основною пам'яттю мікроЕОМ відбувається без участі процесора. Обміном в режимі ПДП керує не програма, яка виконується процесором, а електронні схеми, зовнішні по відношенню до процесора. Зазвичай схеми, що керують обміном в режимі ПДП, розміщуються в спеціальному контролері, який називається контролером прямого доступу до пам'яті.

Обмін даними в режимі ПДП дозволяє використовувати в мікроЕОМ швидкодіючі зовнішні запам'ятовуючі пристрої, такі, наприклад, як накопичувачі на жорстких магнітних дисках, оскільки ПДП може забезпечити час обміну одним байтом даних між пам'яттю і ВЗУ, рівне циклу звернення до пам'яті.

Існують два різновиди прямого доступу до пам'яті з "захопленням циклу". Найбільш простий спосіб організації ПДП полягає в тому, що для обміну використовуються ті машинні цикли процесора, в яких він не обмінюється даними з пам'яттю. У такі цикли контролер ПДП може обмінюватися даними з пам'яттю, не заважаючи роботі процесора. Однак виникає необхідність виділення таких циклів, щоб не сталося тимчасового перекриття обміну ПДП з операціями обміну, ініційованими процесором. У деяких процесорах формується спеціальний керуючий сигнал, який вказує цикли, в яких процесор не звертається до системного інтерфейсу. При використанні інших процесорів для виділення таких циклів необхідне застосування в контролерах ПДП спеціальних селектірующіх схем, що ускладнює їх конструкцію. Застосування розглянутого способу організації ПДП не знижує продуктивності мікроЕОМ, але при цьому обмін в режимі ПДП можливий лише у випадкові моменти часу одиночними байтами або словами.

Найбільш поширеним є ПДП з "захопленням циклу" і примусовим відключенням процесора від шин системного інтерфейсу. Для реалізації такого режиму ПДП системний інтерфейс мікроЕОМ доповнюється двома лініями для передачі керуючих сигналів "Вимога прямого доступу до пам'яті" (ТПДП) і "Надання прямого доступу до пам'яті" (ППДП).

Керуючий сигнал ТПДП формується контролером прямого доступу до пам'яті. Процесор, отримавши цей сигнал, припиняє виконання чергової команди, перш ніж вона закінчиться, видає на системний інтерфейс управляючий сигнал ППДП і відключається від шин системного інтерфейсу. З цього моменту всі шини системного інтерфейсу управляються контролером ПДП. Контролер ПДП, використовуючи шини системного інтерфейсу, здійснює обмін одним байтом або словом даних з пам'яттю мікроЕОМ і потім, знявши сигнал ТПДП, повертає управління системним інтерфейсом процесору. Як тільки контролер ПДП буде готовий до обміну наступним байтом, він знову "захоплює" цикл процесора і т.д. У проміжках між сигналами ТПДП процесор продовжує виконувати команди програми. Тим самим виконання програми сповільнюється, але в меншій мірі, ніж при обміні в режимі переривань.

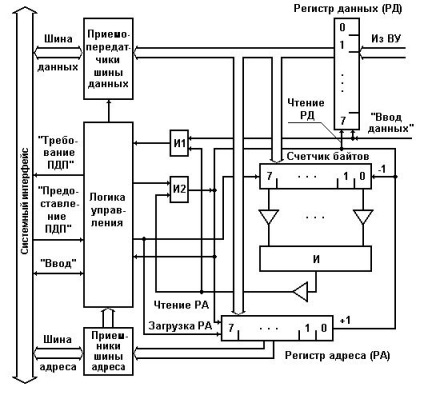

Блок-схема простого контролера ПДП, що забезпечує введення даних в пам'ять мікроЕОМ з ініціативи ВУ в режимі ПДП "Захоплення циклу", наведена на рис. 1.

Мал. 1. Контролер ПДП для введення даних з ВУ в режимі "Захоплення циклу" і відключенням процесора від шин системного інтерфейсу

На прикладі простого контролера ПДП ми розглянули тільки процес підготовки контролера і безпосередньо передачу даних в режимі ПДП. На практиці будь-який сеанс обміну даними з ВУ в режимі ПДП завжди ініціюється програмою, виконуваної процесором, і включає два наступних етапи.

1. На етапі підготовки ВУ до чергового сеансу обміну процесор в режимі програмно-керованого обміну опитує стан ВУ (перевіряє його готовність до обміну) і посилає в ВУ команди, що забезпечують підготовку ВУ до обміну. Така підготовка може зводитися, наприклад, до переміщення головок на необхідну доріжку в накопичувачі на жорсткому диску. Потім виконується завантаження регістрів контролера ПДП. На цьому підготовка до обміну в режимі ПДП завершується і процесор перемикається на виконання іншої програми.

2. Обмін даними в режимі ПДП починається після завершення підготовчих операцій в ВУ з ініціативи або ВУ, як це було розглянуто вище, або процесора. У цьому випадку контролер ПДП необхідно доповнити регістром стану і управління, вміст якого буде визначати режим роботи контролера ПДП. Один з розрядів цього регістра буде ініціювати обмін даними з ВУ. Завантаження інформації в регістр стану і управління контролера ПДП проводиться програмним шляхом.

Найбільш поширеним є обмін в режимі прямого доступу до пам'яті з блокуванням процесора. Він відрізняється від ПДП з "захопленням циклу" тим, що управління системним інтерфейсом передається контролеру ПДП нема на час обміну одним байтом, а на час обміну блоком даних. Такий режим ПДП використовується в тих випадках, коли час обміну одним байтом з ВУ можна порівняти з циклом системної шини.

У мікроЕОМ можна використовувати кілька ВУ, що працюють в режимі ПДП. Надання таким ВУ шин системного інтерфейсу для обміну даними проводиться на пріоритетній основі. Пріоритети ВУ реалізуються так само, як і при обміні, даними в режимі переривання, але замість керуючих сигналів "Вимога переривання" і "Надання переривання" використовуються сигнали "Вимога прямого доступу" і "Надання прямого доступу", відповідно.

Контролер прямого доступу до пам'яті КР580ІК57 (КР580ВТ57)

Обміном даними в комп'ютері при класичному його побудові завідує процесор. Однак таке завдання, як обмін даними з периферійними пристроями (т. Е. При здійсненні зв'язку із зовнішнім світом), намагаються по можливості виконати за допомогою спеціалізованих пристроїв обміну інформацією. Це дозволяє, з одного боку, звільнити процесор (а заодно і програміста) від виконання даного завдання, з іншого - зробити необхідний обмін даними з більшою швидкістю, ніж це міг би зробити процесор. Адже периферійні пристрої здатні працювати зі швидкістю, порівнянної з швидкодією процесора. До таких пристроїв відносяться, наприклад, контролер дисплея або накопичувачі на гнучкому або жорсткому магнітних дисках. Всі вони вимагають наявності в системі так званого контролера прямого доступу до пам'яті, що дозволяє замінити процесор і організувати більш швидкий і прямий обмін даними між пам'яттю і заданим периферійним пристроєм.

Використання БІС ПДП дозволяє істотно скоротити апаратні витрати при реалізації прямого доступу до пам'яті.

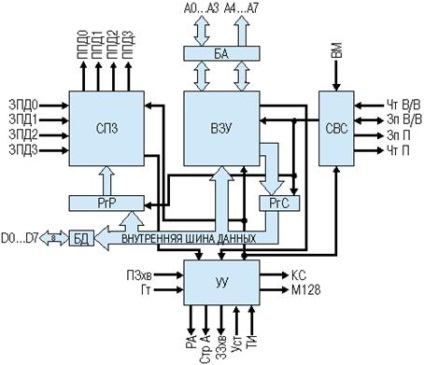

На рис. 2 приведена структурна схема КР580ІК57, в табл. 1 - призначення висновків.

Мал. 2. Структура мікросхеми КР580ІК57

Таблиця 1. Призначення висновків

Схема прийому запитів СПЗ призначена для прийому і прив'язки несинхронних сигналів запитів на організацію прямого доступу до пам'яті від чотирьох пристроїв, а також видачі відповідних сигналів підтвердження. Кожен з чотирьох каналів пов'язаний з БІС ПДП окремими лініями запитів і підтвердження прямого доступу. Видача відповідного сигналу підтвердження для відповідного каналу відбувається в залежності від його пріоритету.

Послідовністю операцій протягом циклів ПД управляє пристрій управління УУ.

Схема вироблення сигналів Запис-Читання СВС здійснює прийом, формування і видачу сигналів, що забезпечують обмін інформацією між процесором і мікросхемою - з одного боку, і пам'яттю і периферійними пристроями - з іншого.

Регістр установки режимів РГР зберігає інформацію про режими роботи БІС, до яких відносяться "Автозавантаження", "Кінець рахунку-стоп", "Подовжена запис", "Звичайна запис", "Циклічний зсув пріоритету" і "Фіксований пріоритет".

РГР зазвичай завантажується після установки РДА та РГЦ і скидається подачею сигналу Уст.

Розряди 0. 3 РГР дозволяють роботу відповідного каналу. Розряди 4. 7 забезпечують відповідний режим роботи БІС. Так, під час запису "1" в розряд 4 РГР пріоритет кожного каналу змінюється.

Обслужений канал матиме найнижчий пріоритет. Порядок обслуговування каналів установливается відповідно до їх номерами 0 >> 1> 2> 3> 0. Якщо розряд 4 РГР встановлений в "0", то кожен канал буде мати фіксований пріоритет. Так, канал 0 має найвищий пріоритет, а канал 3 - найнижчий. При записи "1" в розряд 5 РГР встановлюється режим "Подовжена запис". В цьому режимі тривалість сигналів ЗПП і Зп В / В збільшується при відсутності сигналу готовності зовнішнього пристрою. При цьому БІС входить в стан очікування.

При записи "1" в розряд 6 РГР встановлюється режим "Кінець рахунку - стоп". У цьому випадку після появи сигналу КС обслужений канал виявиться забороненим. Якщо необхідно продовжити обслуговування даного каналу, перепрограмують його розряд дозволу. При "0" в розряді РГР поява сигналу КС не забороняє повторне обслуговування каналу.

При "1" в розряді 7 РГР встановлюється режим "Автозавантаження", що дозволяє каналу 2 повторно пропустити масив даних або зв'язати ряд масивів без програмного втручання.

Регістри каналу 3 зберігають інформацію для переустановлення регістрів каналу 2. Після передачі першого масиву і появи сигналу К.С вміст регістрів каналу 3 передається у відповідні регістри каналу 2. Кожен раз, коли в регістрах каналу 2 відбувається "підміна" даних інформацією регістрів каналу 3, встановлюється розряд "Прапор поновлення даних" в регістрі стану каналів.

Регістр стану каналів РГС вказує номер каналу, який досяг кінця рахунку. Крім того, в РГС входить розряд "Прапор поновлення даних", описаний вище.

В процесі функціонування в складі мікропроцесорної системи мікросхема може перебувати в одному з наступних станів: вихідному, програмування, очікування, обслуговування.

У початковий стан мікросхему переводить зовнішній сигнал Уст. У цьому стані маскуються всі запити каналів ПД, а буфери А0. А3 переводяться в стан прийому інформації. У стані програмування МП має доступ до внутрішніх регістрів обраного каналу відповідно до табл. 2 і 3.

У стані очікування мікросхема знаходиться або від моменту закінчення програмування до видачі сигналу ППД, або в проміжках між циклами ПД.

Після отримання від МП сигналу ПЗхв при наявності сигналу запиту мікросхема виробляє сигнал ППД і переходить в стан обслуговування, в якому системні шини знаходяться під управлінням БІС ПДП.

A3 A2 A1 A0 Операція Регістр

0 0 0 1 Зп Канал 0, кількість циклів

0 0 1 1 Зп Канал 1, кількість циклів

0 1 0 1 Зп Канал 2, кількість циклів

0 у середньому 1 1 + 1 Зп Канал 3, кількість циклів

1 0 0 0 Чт Читання РГС

1 0 0 0 Зп Запис в РГР

Послідовність програмування контролера

Для початку слід запрограмувати РДА та РГЦ вибраного каналу (або обраних каналів).

Усе. Тепер контролер ПДП циклічно пересилає область пам'яті 76D0H-7FF3H в контролер дисплея, припиняючи на цей час роботу процесора.

Всі матеріали в розділі "Інформатика"