Одним із способів обміну даними з ВУ є обмін в режимі прямого доступу до пам'яті (ПДП). В цьому режимі обмін даними між ВУ і основною пам'яттю мікроЕОМ відбувається без участі процесора. Обміном в режимі ПДП керує не програма, яка виконується процесором, а електронні схеми, зовнішні по відношенню до процесора. Зазвичай схеми, що керують обміном в режимі ПДП, розміщуються в спеціальному контролері, який називається контролером прямого доступу до пам'яті.

Обмін даними в режимі ПДП дозволяє використовувати в мікроЕОМ швидкодіючі зовнішні запам'ятовуючі пристрої, такі, наприклад, як накопичувачі на жорстких магнітних дисках, оскільки ПДП може забезпечити час обміну одним байтом даних між пам'яттю і ВЗУ, рівне циклу звернення до пам'яті.

Існують два різновиди прямого доступу до пам'яті з "захопленням циклу". Найбільш простий спосіб організації ПДП полягає в тому, що для обміну використовуються ті машинні цикли процесора, в яких він не обмінюється даними з пам'яттю. У такі цикли контролер ПДП може обмінюватися даними з пам'яттю, не заважаючи роботі процесора. Однак виникає необхідність виділення таких циклів, щоб не сталося тимчасового перекриття обміну ПДП з операціями обміну, ініційованими процесором. У деяких процесорах формується спеціальний керуючий сигнал, який вказує цикли, в яких процесор не звертається до системного інтерфейсу. При використанні інших процесорів для виділення таких циклів необхідне застосування в контролерах ПДП спеціальних селектірующіх схем, що ускладнює їх конструкцію. Застосування розглянутого способу організації ПДП не знижує продуктивності мікроЕОМ, але при цьому обмін в режимі ПДП можливий лише у випадкові моменти часу одиночними байтами або словами.

Найбільш поширеним є ПДП з "захопленням циклу" і примусовим відключенням процесора від шин системного інтерфейсу. Для реалізації такого режиму ПДП системний інтерфейс мікроЕОМ доповнюється двома лініями для передачі керуючих сигналів "Вимога прямого доступу до пам'яті" (ТПДП) і "Надання прямого доступу до пам'яті" (ППДП).

Керуючий сигнал ТПДП формується контролером прямого доступу до пам'яті. Процесор, отримавши цей сигнал, припиняє виконання чергової команди, перш ніж вона закінчиться, видає на системний інтерфейс управляючий сигнал ППДП і відключається від шин системного інтерфейсу. З цього моменту всі шини системного інтерфейсу управляються контролером ПДП. Контролер ПДП, використовуючи шини системного інтерфейсу, здійснює обмін одним байтом або словом даних з пам'яттю мікроЕОМ і потім, знявши сигнал ТПДП, повертає управління системним інтерфейсом процесору. Як тільки контролер ПДП буде готовий до обміну наступним байтом, він знову "захоплює" цикл процесора і т.д. У проміжках між сигналами ТПДП процесор продовжує виконувати команди програми. Тим самим виконання програми сповільнюється, але в меншій мірі, ніж при обміні в режимі переривань.

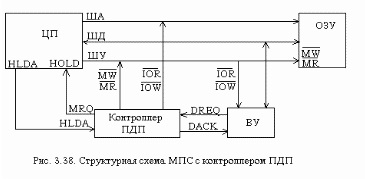

Режим ПДП є самим скорост-ним способом обміну, який реалізується за допомогою спеціальних апаратних засобів - контролерів ПДП без використання програмного забезпечення. Для осу-ществления режиму ПДП контролер повинен виконати ряд послідовних опера-цій (рис. 3.38):

прийняти запит DREQ на ПДП від ВУ;

сформувати запит HRQ на захоплення шин для ЦП;

прийняти сигнал HLDA, що підтверджує цей факт після того, як ЦП виття-дет в стан захоплення (ШД, ША, ШУ в z-стан);

сформувати сигнал DACK, повідомляє ВУ про початок виконання циклів ПДП;

виробити сигнали забезпечують управління обміном;