Екстремальну підсистему зберігання даних на основі двох плат рас-ши-ре-ня ASUS Hyper M.2 x16. обслуговуючу в цілому по-сім NVMe-пристроїв, можна розглядати як перші кроки по ор-га-ні-за-ції VMD RAID-масивів. Потенціал нової архітектури в пер-спек-ти-ве по-зво-ля-ет го-во-рить про сторідж в десятки і сотні накопичувачів з прицілом на ви-со-ко-у-рів-ні-ші сервери. А тому завдання фізичного підключення і оп-ти-маль-но-го дизайну PCIe-топології набуває осо-буя актуальність. Ра-зум-но припустити, що в платформах для ен-ту-зи-ас-тов і серверному сег-мен-ті ре-шать-ся вона буде по-різному.

ASUS Hyper M.2 x16

Реалізація концепції Intel VROC with VMD Technology в пристрої ASUS Hyper M.2 x16 має на увазі під-лю-че-ня розміщених на платі-адаптер чотирьох NVMe-накопичувачів до порту PCIe x16. Кожному з накопичувачів плата Hyper надає лінк PCIe Gen3 x4. В умовах мінімуму офіційної інформації, спробуємо смо-де-лі-ро-вать два варіанти розвитку подій, які представляють компроміси продуктивності, сумісності і, ко-неп-но, вартості новітніх рішень.

Власницьке рішення на основі CPU PCIe bifurcation

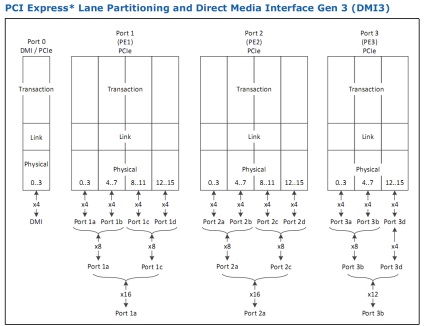

Діаграма нижче (Рис 1) показує варіанти конфігурації до 44 PCIe-лінків процесорів Intel Core X-серії. Порт DMI (Direct Media Interface), який використовується для зв'язку CPU і системної логіки, не входить до цього числа і по-ка-че окремо (зліва), хоча також реалізований у вигляді лінка PCIe x4.

Рис 1.Діаграмма показує підтримувані варіанти біфуркації до 44PCIe-лінків для процессоровIntelCoreX-Seriesс разделеніемPCIe-портовx16 іx12 на кілька портів меншою ширини (фрагмент документацііIntelCoreX-SeriesProcessorFamilies)

Очевидно, гнучкість конфігурації ресурсів CPU, зокрема, - здатність PCIe-портів до біфуркації (раз-де-ле-нию на порти меншою ширини), спрощує завдання розробників платформ, роблячи непотрібними зовнішні кому-го-та-ци-он-ні елементи, мінімізується як вартість плати-адаптера, так і латентність доступу до ад-ре-су-е-мим ре-сур-сам.

Разом з тим, подібне рішення оптимально для компонентів, встановлених безпосередньо на системну плату, топологія і функціональність яких заздалегідь відома і не може бути змінена, або для поділу лінків між PCIe-слотами, але не в межах одного слота.

Строго кажучи, розробник плати-адаптера PCIe x16 не має права ставити працездатність пристрою в за-ві-сі-ність від здатності x16-порту до біфуркації. адже така здатність не нормується стандартом як зо-за-тель-ва. Це означає, що пристрій оптимально використовує можливості деякої приватної конфігурації, але його працездатність залежить від виробника і моделі системної плати, процесора і навіть використовуваного слота PCIe.

Стандартне рішення на основі PCIe-switch

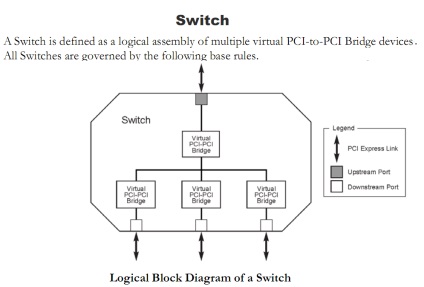

Згідно зі специфікацією PCI Express, уніфіковане рішення, що забезпечує розгалуження шини, ос-но-ви-ва-ет-ся на застосуванні PCIeSwitch. Такий комутатор визначається як набір віртуальних мостів PCI-to-PCI. Вір-ту-аль-ність в даному випадку означає дотримання вимог програмної моделі PCI-PCI Bridge, в той час, як право вибору внутрішньої фізичної реалізації залишається за розробником електронного приладу.

Рис 2. Визначення устройстваSwitch, що застосовується для розгалуження топологііPCIe

(Фрагмент документаPCIExpressBaseSpecificationRevision4.0)

Встановивши на платі-адаптер дискретний PCIe-switch, розробник реалізує стандартний пристрій PCIe x16, усуваючи залежність від недокументованою спроможності порту x16 виконати поділ на чотири порти x4.

VMD в серверному контексті

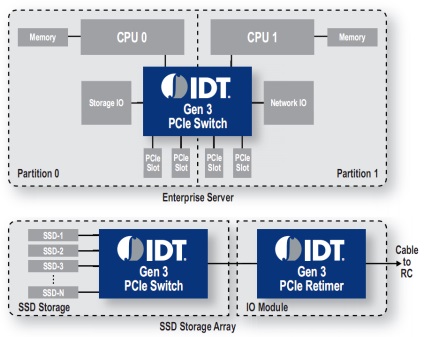

Для шинної топології високорівневих серверів і робочих станцій застосування додаткових кому-го-та-ци-ОНН-их пристроїв є необхідністю, а не опцією.

Рис 3.Топологія високорівневою мультипроцессорной платформи, що використовує комутатори для подключеніяmassstorageподсістеми (фрагмент документацііIDT89H64H16G3 64-Lane16-PortPCIeGen3SystemInterconnectSwitch)

Перерахуємо чотири ситуації, що вимагають установки додаткових дискретних компонентів, що розширюють функціональність PCIe-підсистеми.

- Доступна кількість диференціальних пар PCIe фізично недостатньо для підключення необхідної кількості NVMe-пристроїв.

- Платформа має необхідну кількість диференціальних пар; біфуркація PCIe-порту забезпечує підключення заданої кількості пристроїв, але входить в протиріччя з вимогами сумісності для плати-адаптера.

- Необхідно забезпечити доступність дискового масиву для декількох процесорів (Рис 3). Розглядаючи цей приклад, акцентуємо увагу на тому, що процесори, спільно використовують фрагмент PCIe-топології можуть бути розташовані на різних платформах і не пов'язані шиною межпроцессорной зв'язку (QPI), що створює обхідний шлях.

- Геометричні особливості системи (довжина сполучних провідників і кількість рознімних з'єднань) вимагають відновлення електрофізичних характеристик сигналів за допомогою ретаймер і редрайверов.

замість післямови

Підвищувати собівартість пристроїв, одночасно жертвуючи продуктивністю і уніфікуючи рішення в це-лях сумісності з виробами конкурентів, - крок, в сучасних умовах кілька ексцентричний. А значить, для SOHO екстремальних платформ. пріоритет повинен належати першому пропрієтарного варіанту, «ви-жи-ма-ющему максимум» з розширених можливостей CPU PCIe-портів.

У той час як для високорівневих серверів і робочих станцій. «Іграшкові» рішення такого роду не-прі третьому-ле-ми. Тут слід очікувати реалізацій другого уніфікованого варіанту, що поєднує функціональність VMD RAID і зовнішніх комутаторів.