Перепрошивка SPD мікросхеми на планці ОЗУ

SPD і програматор

Зараз часто зустрічаються модулі, які мають занижені параметри. Також зустрічаються материнські плати, які визначають тип пам'яті і жорстко забороняють встановлювати частоту пам'яті велику записаної в SPD. Так, наприклад, при установці модуля DDR333 в материнські плати MSI K8N Neo, EPoX 8KDA3 (+ # 92; J # 92; I) та інші максимальна частота пам'яті обмежена 333 МГц (без розгону), хоча модуль можливо здатний стабільно працювати на більш високих частотах. Домогтися частоти пам'яті рівний частоті HT традиційними методами немає ніякої можливості. Для цього доводилося використовувати програму A64 Tweaker, яка може не завжди стабільно працювати на різних платформах. Тому виникла потреба в програмуванні SPD. Перетворивши DDR333 в DDR400, ми легко вирішуємо цю проблему, і розгін у нас обмежать лише самі чіпи пам'яті або процесор.

Сенс використання SPD чітко зрозумілий для виробника, як модулів пам'яті, так і материнських плат, однак для кінцевого користувача за великим рахунком інтересу не уявляв. Наявність схеми послідовного детектування на модулі пам'яті позбавляє виробників материнських плат від необхідності вносити оптимальні значення основних часових параметрів в системний BIOS (як це робить, наприклад, Intel, використовуючи в своїх материнських платах Phoenix BIOS), оскільки вся необхідна інформація для нормальної настройки підсистеми і її стабільного функціонування міститься в мікросхемі SPD. Крім цього, механізм SPD може налаштувати систему і гарантувати більш-менш стійку роботу при використанні в підсистемі пам'яті модулів різної організації, різного об'єму і мають різні значення однойменних параметрів. Все, що потрібно зробити контролера - це при ініціалізації системи вважати записані в SPD дані.

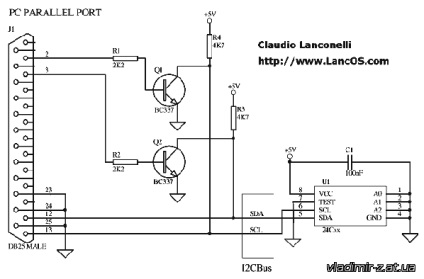

Для програмування SPD був використаний наступний "адаптер-програматор":

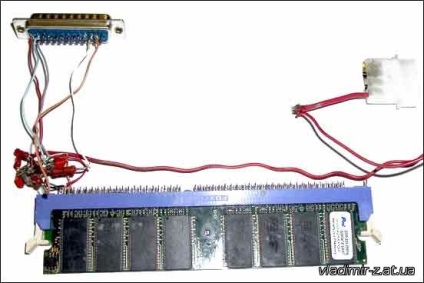

Збірка даного пристрою не повинна викликати будь-яких ускладнень для людей бачили паяльник і транзистор. Транзистори можна використовувати будь-які типи n-p-n, в нашому випадку це були KT315Б і BC817 в SMD корпусі. Вид програматора може бути таким (це тестовий прототип, тільки для того, щоб переконається, що все працює):

Я використовував DDR DIMM роз'єм з материнської плати для більшої зручності при прошивці великої кількості модулів. Також перевага даного підходу в збереженні гарантійного виду модулів пам'яті. Однак можна і безпосередньо підпаяти дроти до EEPROM на платі, що не випаюючи її. Всі необхідні сигнали виведені на роз'ємі DDR DIMM. EEPROM встановлена на платі модуля має висновки A0, A1, A2, WP (TEST) з'єднані з землею (GND).

DDR DIMM pad №93

Ну а ті ж, хто вважає таку конструкцію ненадійною і небезпечною може зробити плату, Наприклад, як мій біль:

Не поспішайте відразу припаювати чіп до програматора, спочатку увімкніть його окремо. Якщо у вас все спаяно вірно і нічого не вибухнуло, перевірте кабель і тільки потім, вимкнувши схему, припаював чіп або плату. Так само не варто використовувати великі паяльники потужністю більше 25 Вт, інакше є можливість спалити деталі.

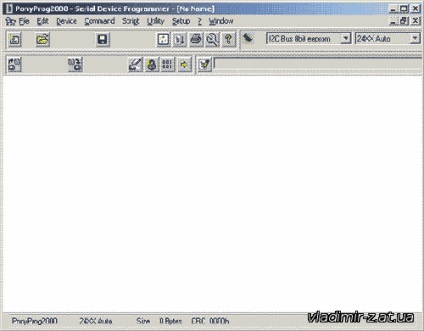

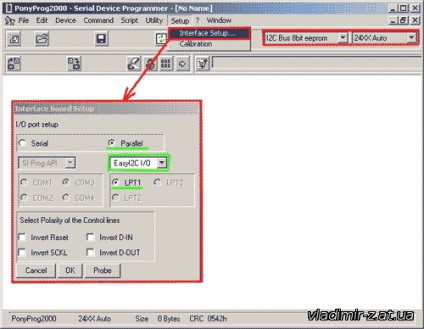

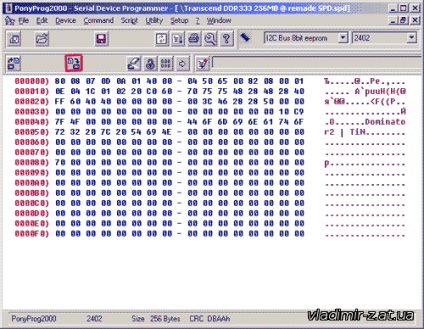

Початкове налаштування полягає в наступному: необхідно вибрати тип прошивається пам'яті - I2C Bus 8bit EEPROM, а мікросхему - 24XX Auto або 2402. Це робиться за допомогою меню, що випадають у верхній правій частині. Потім в меню Setup> Interface Setup. потрібно встановити тип програматора, який використовується. У нашому випадку це EasyI2C I / O. Оскільки цей програматор має паралельний інтерфейс, слід вибрати порт LPT1. В кінцевому вигляді все повинно бути в точності як на скріншоті нижче:

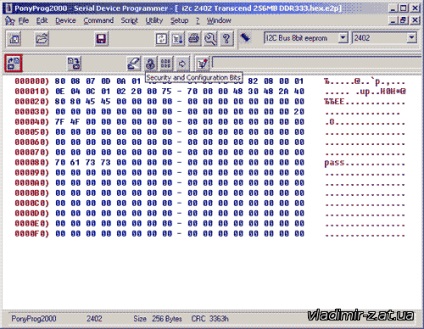

Тепер необхідно підключити програматор з підключеною мікросхемою і вважати її. Для цього призначена кнопка Read Device. Після вдалої процедури читання у вас має бути на екрані щось схоже:

Якщо ж у вас модуль не зважав, перевірте правильність складання, можливо, ви переплутали сигнали SCL і SDA.

Параметр контролера пам'яті - DRAM Command Rate

Сама здатність обробки команд з затримкою 1T залежить від таких факторів, як частота синхронізації шини пам'яті, кількість мікросхем на модулі пам'яті (чим більше мікросхем, тим більше часу знадобиться контролера, щоб вибрати необхідну), якість використовуваного модуля, загальна кількість використовуваних модулів пам'яті в системі (прямо пов'язане з кількістю мікросхем в складі одного модуля) і віддаленість модуля від контролера (протяжність сигнальних трас від висновків контролера до висновків мікросхеми пам'яті з урахуванням кількості пров еходов).

Таким чином, якщо в системі з процесором на ядрах SledgeHammer, ClawHammer, NewCastle, Winchester використовується два 2-банкових модуля, необхідно використовувати 2Т, інакше сигнали доходять з помилками. Пізніше буде проаналізовано вплив цього параметра на швидкість в цілому. У процесорах на ядрі Venice і наступних можливе використання параметра 1Т в системі з 4-ма банками пам'яті без втрати стабільності.

У даній статті не буде наведено докладний опис інших таймінгів, тому що мета дослідження полягала в з'ясуванні максимально продуктивного режиму для платформи Аthlon 64, а не вивченні пам'яті. Якщо ж буде потрібно детальна інформація про таймингах зверніться до статті "Налаштування підсистеми пам'яті в BIOS SETUP".