Дякую вам за підтримку!

Конфігурація тестових стендів

Стенд №1 (без «заплатки»)

Стенд №2 (з «латкою»)

Реальна пропускна здатність кешу даних / пам'яті

Насамперед зазначимо, що наведені в цьому дослідженні абсолютні результати тестів платформи AMD Phenom X4 з «латкою» можуть дещо відрізнятися від тих, що були отримані раніше (без «заплатки») щодо використання різних материнських плат (див. Конфігурацію тестових стендів). Зокрема, на момент дослідження першої системи (стенд №1, материнська плата MSI K9A2 Platinum) не було відомо, яка саме частота північного моста і L3-кеша процесора виставляється за замовчуванням на цій системі. На розглянутій в цій статті другої системі (стенд №2, материнська плата Gigabyte MA790GX-DQ6) утиліта AMD Overdrive показала, частота контролера пам'яті і L3-кеша процесора за замовчуванням встановлюється рівною 2.0 ГГц при частоті ядер процесора 2.4 ГГц. Розумно припустити, що такий же режим «за замовчуванням» використовується і на першій з досліджених нами материнських плат. У цьому ж дослідженні ми збільшили частоту північного мосту процесора до 2.4 ГГц вручну за допомогою налаштувань BIOS Setup для забезпечення синхронності функціонування ядер процесора і його інтегрованого контролера пам'яті, і порівняння такого режиму роботи процесора з режимом роботи «за замовчуванням» (CPU 2.4 ГГц, NB 2.0 ГГц).

Результати вимірювання пропускної здатності (ПС) кешей даних процесора і оперативної пам'яті приведені в табл. 1.

Середня реальна пропускна здатність, байт / такт

5.23 ГБ / с (40.9%)

3.43 ГБ / с (26.8%)

* В дужках вказані значення щодо теоретичної межі ПС шини пам'яті

Як і слід було очікувати, швидкісні характеристики L1- і L2-кешей даних ядра процесора при використанні «заплатки» не змінюються. Швидкісні характеристики L3-кеша на другий системі дещо зростають (на 8-11%), тоді як швидкісні характеристики підсистеми пам'яті помітно знижуються (особливо, ПСП на читання, приблизно на 18%). Уже з результатів цього тесту можна зробити попередній висновок про те, що застосування «заплатки» не робить істотного впливу на L3-кеш процесора (при цьому його ПС збільшується в зв'язку зі збільшенням його частоти з 2.0 до 2.4 ГГц, хоча приріст ПС виявляється менше по порівняно з 20% приростом частоти), але впливає на ПСП (незважаючи на збільшення тактової частоти контролера пам'яті). Справедливість твердження про відсутність впливу «заплатки» на характеристики L3-кеша підтвердиться подальшими тестами.

Гранична реальна пропускна здатність пам'яті

Граничні характеристики реальної ПСП, наведені в табл. 2, в разі застосування «заплатки» також виявляються нижчими: максимальна реальна ПСП на читання знижується на 19.5%, на запис - приблизно на 4.5%.

18.2 нс

18.6 нс

39.0 нс

225.8 нс

* Розмір блоку 32 МБ

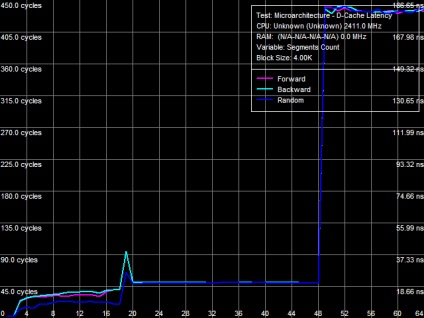

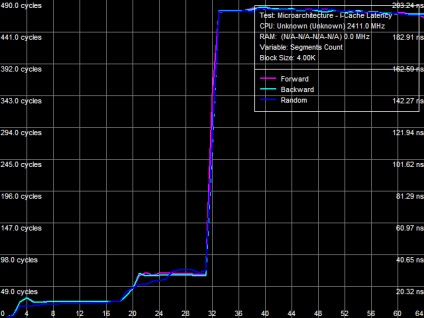

Кількісні характеристики латентності L1-, L2- і L3-кешей, представлені в табл. 3, демонструють практично повну незмінність при застосуванні «заплатки», що знову підтверджує відсутність впливу «заплатки» на L3-кеш процесора. А зрослі величини латентності пам'яті (приблизно на 13% при псевдовипадковому доступі, і більш ніж в 2.6 разів (!) При випадковому доступі) свідчать про значне погіршення швидкісних характеристик останньої в умови промаху L2 D-TLB ядра процесора (тобто в тому випадку, коли ці промахи повинні «маскуватися» недокументованою структурою «TLB» контролера пам'яті процесора, відключеною при застосуванні «заплатки»).

Мінімальна латентність кеша даних і пам'яті

Висновки, зроблені щодо значень середньої латентності кеша даних і пам'яті, можна повністю поширити і на випадок мінімальних значень латентності, представлених в табл. 4. Характерно відзначити деяке зниження ефективності апаратної передвибірки, що виявляється в збільшенні латентності пам'яті при прямому і зворотному обході при застосуванні «заплатки», хоча це і не можна вважати прямим наслідком відключення «TLB» контролера пам'яті процесора.

Рівень, режим доступу

Мінімальна латентність, тактів (нс)

* Розмір блоку 32 МБ

** в дужках вказані значення, отримані методом №2

Асоціативність кеша даних

Результат вимірювання асоціативності L1-, L2- і L3-кеша даних (рис. 2) не має відмінностей з точки зору самих значень асоціативності кеша, але відрізняється істотним штрафом «промаху по асоціативності» всіх рівнів кешу, що спостерігається при використанні більше 48 сегментів кеша. Цей ефект, очевидно, є родинним ефекту промаху L2 D-TLB, коли латентності звернення до пам'яті повинні маскуватися TLB контролера пам'яті.

Мал. 2. Асоціативність кеша даних

Реальна пропускна здатність шини L1-L2 кешу

Як і середня реальна ПС L2-кеша, реальна ПС шини L1-L2 (див. Табл. 5) теж зазнає змін при використанні «заплатки».

Реальна пропускна здатність L1-L2, байт / такт

Phenom X4 без «заплатки»

Phenom X4 з «латкою»

Читання (пряме)

Читання (зворотне)

Запис (пряма)

Запис (зворотна)

Реальна пропускна здатність шини L2-L3 кешу

Що стосується реальної ПС шини L2 (ядро процесора) -L3 (контролер пам'яті), її швидкісні характеристики (див. Табл. 6), як і виміряна раніше ПС L3-кеша, на даній системі виявляються трохи вище (приблизно на 8%) в зв'язку з більш високою частотою контролера пам'яті процесора (2.4 проти 2.0 ГГц).

Реальна пропускна здатність L2-L3, байт / такт

Phenom X4 без «заплатки»

Phenom X4 з «латкою»

Читання (пряме)

Читання (зворотне)

Запис (пряма)

Запис (зворотна)

Кеш інструкцій, реальна пропускна здатність декодування / виконання коду

Очевидно відсутність впливу «заплатки» і на швидкість декодування / виконання інструкцій з L1-I, а також L2-кеша ядра процесора (див. Табл. 7). У той же час, швидкість виконання коду з L3-кеша знову зростає (приблизно на ті ж 8%, що і ПС L3-кеша) у зв'язку зі збільшенням частоти останнього з 2.0 до 2.4 ГГц.

Тип інструкцій

(Розмір, байт)

Реальна пропускна здатність декодування / виконання, байт / такт (інструкцій / такт)

Асоціативність кеша інструкцій

Тест асоціативності кеша інструкцій (рис. 3) показує досить цікаву картину. А саме, на ній зникає виявлений в попередній серії тестів (без «заплатки») другий перегин асоціативності L3-кеша в області приблизно 50 сегментів кеша. У той же час, як і в тесті асоціативності кеша даних, значно зростає штраф «промаху по асоціативності» останнього рівня кешу процесора. Звідси можна зробити висновок про те, що ефективна асоціативність L3-кеша при кешуванні коду дорівнює 14 (32 за вирахуванням 18), а раніше спостерігається другий перегин в області 50 сегментів є артефактом.

Мал. 3. Асоціативність кеша даних

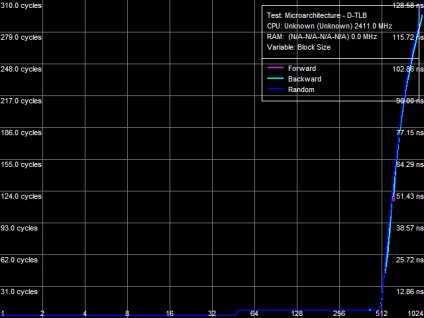

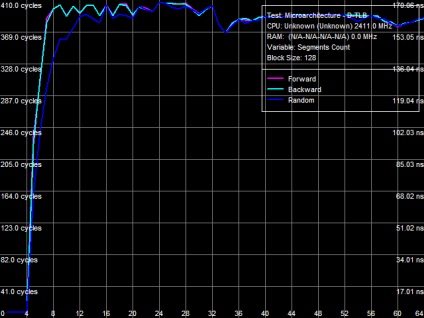

характеристики TLB

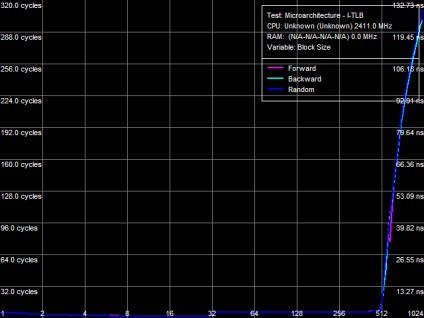

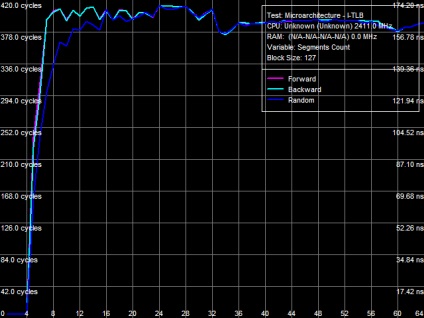

Як і слід було очікувати, найбільший ефект від включення «заплатки» демонструють тести TLB процесора. Природно, при цьому самі характеристики TLB ніяк не змінюються (оскільки ці елементи архітектури відносяться до ядра процесора), але істотно зростає штраф промаху останнього рівня TLB як «за розміром», так і «по асоціативності».

Мал. 4. Розмір D-TLB

Мал. 5. Асоціативність L2 D-TLB

На рис. 4 представлений результат тесту розміру D-TLB, а на рис. 5 - тест асоціативності L2 D-TLB. В обох випадках у наявності істотне зростання штрафу промаху L2 D-TLB - приблизно 290 тактів при вичерпанні його обсягу і до 400 тактів при вичерпанні його асоціативності.

Мал. 6. Розмір I-TLB

Мал. 7. Асоціативність L2 I-TLB

Аналогічний результат показують тести розміру (рис. 6) і асоціативності (рис. 7) I-TLB. Штраф промаху L2 I-TLB «за розміром» становить приблизно 300 тактів, а «по асоціативності» - близько 400 тактів, що близько до відповідним величинам, отриманим в тестах D-TLB.

Які ж висновки можна зробити з результатів зробленого дослідження? Перш за все, очевидний і важливий висновок про те, що процесори сімейства AMD Phenom (K10), а також AMD Athlon 64 (K8) дійсно містять в своєму інтегрованому контролері пам'яті якусь структуру, яку можна вважати буфером TLB досить великого розміру, ефективному як при зверненні до даних (D-TLB), так і при виконанні коду (I-TLB). Існування цієї структури в обох родинах процесорів доводиться помірним порядком величин штрафу промаху останнього рівня (L2) D-TLB і I-TLB ядра процесора, що знаходяться в межах 20-40 тактів. У той же час, її відключення (а це - найбільш розумне пояснення того, як діє «латочка» для процесорів AMD Phenom) призводить до суттєвого зростання розглянутих величин штрафу промаху (до 300-400 тактів, тобто практично на порядок!) . У зв'язку з цим цікаво також згадати «енергоефективні» процесори AMD Athlon 64 X2 EE. в яких штраф промаху L2 D-TLB і I-TLB спочатку є високим. Можна припустити, що в цих процесорах структура «TLB» контролера пам'яті або відсутній зовсім (що малоймовірно, тому що не можна сказати, що вона настільки складна в реалізації та споживає так багато енергії, що її треба було зовсім виключити з «енергоефективних» варіантів процесорів), або ... відключена спочатку внаслідок наявності помилки, схожою з помилкою в контролері пам'яті процесорів Phenom (що набагато більш імовірно).

Наступний висновок, який можна зробити за результатами нашого дослідження, полягає в тому, що згадана вище структура «TLB» відноситься саме до контролера пам'яті процесора, а не його L3-кешу (про що писалося в ранніх повідомленнях про помилку в процесорах Phenom). Це підтверджується практично повною відсутністю негативного впливу «заплатки» на швидкісні характеристики (ПС і латентність) L3-кеша процесора. Таким чином, зниження продуктивності системи в цілому при застосуванні «заплатки» пояснюється виключно зниженням швидкісних характеристик підсистеми пам'яті і, особливо, істотним зростанням латентності випадкового доступу до пам'яті. Для зручності, представимо їх у зведеній таблиці.

Значення без «заплатки»

Значення з «латкою»

Ідея привести якусь усереднену величину ефекту «заплатки» по настільки розрізненим низькорівневим характеристикам представляється досить безглуздою - розкид значень становить від 1.7% до 11.8 раз, а самі ефекти (наприклад, зростання штрафів промаху TLB) не виявляють себе настільки ж значним чином в реальних додатках зважаючи винятковою «синтетичне» самих характеристик. У той же час, в загальну групу можна виділити зниження швидкісних характеристик підсистеми пам'яті (18-20%), досить близьких до реальності, яке виявляється порівнянним із зниженням продуктивності системи в більшості реальних додатків, що оперують з даними радше «потоковим», ніж «випадковим »чином. При випадковому ж доступі до даних можна очікувати і більшого зниження продуктивності системи в цілому, оскільки латентність доступу до пам'яті в такому режимі зростає досить відчутно.

Дмитро Бесєдін