АРХІТЕКТУРА КОНТРОЛЛЕРА ІНТЕРФЕЙСУ ПАМ'ЯТІ SRAM ДЛЯ ЗАБЕЗПЕЧЕННЯ МАКСИМАЛЬНО ПРОДУКТИВНОСТІ комутуючого пристрою

Науково-дослідний інститут системних досліджень РАН, ***** @ *** niisi. *****

Комутатори, побудовані на базі комутаційної матриці, забезпечують найшвидший спосіб взаємодії портів. В такому комутаторі встановлюється з'єднання між портом прийому і портом призначення, по якому передаються дані. Якщо порт призначення зайнятий, дані можуть бути Буферізірованний в процесорі вхідного порту. У комутаторах із загальною шиною процесори портів пов'язують високошвидкісною шиною. Недоліком цих архітектур є те, що ні комутаційна матриця, ні загальна шина не дозволяють буферізіровать дані.

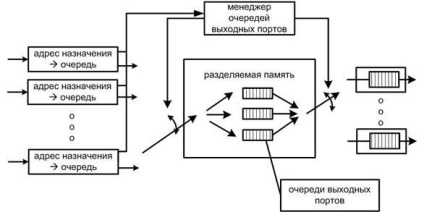

Комутатори з пам'яттю, що використовують блок пам'яті для зберігання комутованих даних, які очікують розрахунку маршруту слідування і / або звільнення порту призначення (Рис. 1).

Мал. 1. Комутатор з пам'яттю

Вхідні блоки процесорів портів з'єднуються з перемикається входом розділяється пам'яті, а вихідні блоки цих же процесорів з'єднуються з перемикається виходом цієї пам'яті. Перемиканням входу і виходу розділяється пам'яті управляє менеджер черг вихідних портів. Такий комутатор має більшу затримкою передачі даних, але меншими втратами даних. У таких комутаторах обробка даних ділиться на три основні дії:

· Прийом даних - процесори вхідних портів записують вхідні пакети даних в пам'ять, що розділяється;

До продуктивності пристрою, що запам'ятовує при такій архітектурі пред'являються особливі вимоги. ЗУ має забезпечити достатню пропускну здатність, щоб вхідні порти встигали отримувати доступ до пам'яті для запису даних без втрат; в той же час вихідні порти повинні вчасно зчитувати дані, щоб не відбулося переривання даних, переданих в середу, до закінчення блоку. Тобто продуктивність ЗУ в рази перевищує продуктивність кожного каналу. Розглянемо вимоги до ЗУ для 6-портового комутатора Gigabit Ethernet. Кожен порт, який працює в повнодуплексному режимі, одночасно приймає і передає дані зі швидкістю 1Гбіт / с. Тобто ЗУ має забезпечувати пропускну здатність 12 Гбіт / с.

У таких системах використовується статична пам'ять SRAM. Така пам'ять має більш простий інтерфейс, хоча її вартість вище. У гіршому випадку 12 портів комутатора звертаються в довільні області пам'яті для запису і читання даних, що вимагає додаткових циклів активації і закриття рядків і циклів регенерації. При використанні компонентів DRAM з конвеєрної обробкою даних, затримка перемикання між довільними рядками становить 2 такту при довжині пакета даних в 4 такту. При такій роботі динамічна пам'ять, що забезпечує необхідну продуктивність комутатора, потребують більшої частоти роботи в порівнянні зі статичною пам'яттю SRAM.

Розміщення блоку пам'яті SRAM на кристалі комутатора пов'язане з великими витратами на розробку / покупку швидкодіючого блоку пам'яті SRAM, а також висуває підвищені вимоги до виробництва мікросхеми, зокрема, вимагає поєднання технології звичайної логіки і пам'яті великих обсягів (для комутатора використовувалося ЗУ обсягом 4 Мбайт) . Використання зовнішньої мікросхеми пам'яті SRAM дозволяє скоротити такі витрати, але вимагає розташування елемента на друкованій платі, використовуваної в системі. Мікросхема комутатора була спроектована для використання з зовнішнім ЗУ SRAM.

Звичайна мікросхема ЗУ типу SRAM з одним 32-бітовим портом для читання / запису, що працює на 200 МГц, дозволяє пропускати 6,4 Гбіт даних в секунду, тобто забезпечує роботу 3х портів. Для створення 6-портового комутатора необхідно збільшити пропускну здатність ЗУ в два рази. Для цього буде потрібно використовувати одну з наступних ЗУ:

· Двухпортовая 32-розрядна пам'ять, що працює на 200 МГц;

· 64-розрядна пам'ять, що працює на 200 МГц;

· Пам'ять DDR (double-data rate) на 200 МГц;

· Однопортовая 32-розрядна пам'ять, що працює на 400 МГц.

Всі ці підходи мають свої переваги і недоліки:

· Використання двухпортовой пам'яті спрощує роботу арбітра пам'яті (що працює на високій частоті), якому тепер потрібно відстежувати і обробляти в два рази менше запитів, але одночасно збільшує кількість сигналів, що виходять з мікросхеми. При цьому двухпортовая пам'ять може бути «істинно» двухпортовой, коли кожен порт ЗУ працює на читання і на запис, або «простий» двухпортовой пам'яттю, коли один порт працює тільки в режимі читання, а другий - тільки записи. Для комутуючого пристрою запити читання і запису розподілені порівну, і такий розподіл функціональності портів ЗУ несуттєво; для інших пристроїв таку пам'ять потрібно вибирати з урахуванням вимог проекту.

· Вибір мікросхеми ЗУ, що працює на частоті 400 МГц, або використання пам'яті DDR пов'язані з технологічними труднощами, оскільки вимагають проектування не тільки внутрішнього логічного блоку, здатного працювати на 400 МГц (що позначається на часі проектування і використовуваної технології виробництва), але і більш складною розробки друкованої плати, використовуваної в системі. Використання пам'яті DDR вимагає невеликого зміни схеми роботи контролера доступу до ЗУ.

Найбільш оптимальним підходом по співвідношенню складність розробки / вартість є збільшення ширини шини даних. При цьому комутатор має один 64х розрядний канал звернення до ЗУ для читання / запису, що працює на частоті 200 МГц (що в підсумку дає 12,8 Гбіт / с), а представлені 6 портів комутатора використовують 12 каналів звернення до пам'яті (для читання і запису ). Контролер доступу до пам'яті обробляє запити портів комутатора на звернення до пам'яті і забезпечує своєчасний і безперервний потік даних.

Для забезпечення низької вартості розробки, необхідно, щоб ядро мікросхеми комутатора працювало на більш низьких частотах - 50-100 МГц. Такі частоти досягаються за допомогою систем автоматизованого проектування з набагато меншими зусиллями, ніж 200-250 МГц, які вимагають від розробника великих тимчасових витрат або використання більш дорогих технологій виробництва.

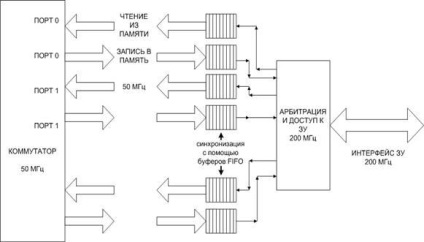

Пропонується архітектура контролера інтерфейсу пам'яті (Рис. 2):

· Блок інтерфейсу пам'яті для роботи на необхідної високої частоти звернень до пам'яті (200-250 МГц);

· «Внутрішні» по відношенню до комутатора інтерфейси пам'яті, що працюють на середньої / необхідній частоті 50-100 МГц;

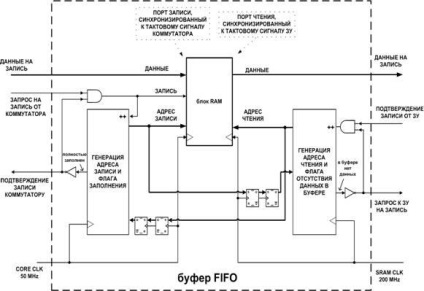

· Буфери синхронізації і підкачки для зв'язування цих двох інтерфейсів.

Однопортова пам'ять SRAM вимагає арбітраціі між 12 каналами запитів. Для рівномірного розподілу доступу портів до ЗУ найкраще підходить циклічне розподіл (Round-Robin Schedule). Для забезпечення необхідної швидкості арбітраціі, робота блоку може бути конвейерізірована і здійснюватися за кілька тактів. При цьому, для зменшення витрат часу на доступ до пам'яті, операції читання / запису вигідніше проводити в пакетному режимі, коли при отриманні доступу до пам'яті один канал послідовно читає / записує кілька слів. У той же час розмір пакета не повинен бути занадто великим, щоб один канал запису або читання не блокував роботу інших портів. У даній роботі доступ до ЗУ здійснювався у вигляді пакетів розміром чотири 64-розрядних слова.

Мал. 2. Схема контролера доступу до ЗУ

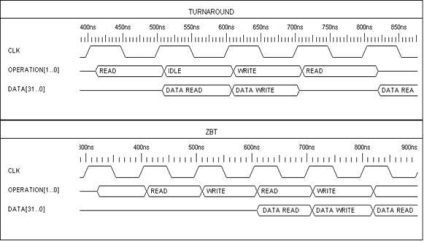

Для мережевих технологій, що вимагають високої швидкості звернення до ЗУ, на ринку представлені компоненти пам'яті ZBT® / NoBL ™ SRAM (Zero Bus Turnaround - нульовий цикл перемикання шини, No Bus Latency - відсутня затримка шини). Така пам'ять забезпечує максимальну пропускну здатність шини за рахунок усунення циклу перемикання між операціями запису і читання (Рис. 4). Пристрої пам'яті ZBT® SRAM працюють як по потокової, так і за конвеєрною технологією. Конвеєрні пристрої працюють на більш високих частотах, а потокові мають меншу затримку даних.

Більшість виробників випускають пам'ять SRAM зі збільшеною шиною даних, що дозволяє записувати і зчитувати додаткові біти побайтовой парності (18/36 розрядна шина даних). При установці двох мікросхем пам'яті з 36 розрядної шиною даних паралельно, доступні 8 додаткових біт дають можливість використовувати надлишкові коди, які виявляють і виправляють помилки. Так, наприклад, код Хеммінга дозволяє виправляти однобітові помилки на шині даних і виявляти помилки в двох бітах. Для 32 розрядів даних код Хеммінга використовує 7 додаткових біт, для 64 розрядів - 8 біт. Кодування / виправлення помилок перед безпосереднім доступом до пам'яті дозволяє уникнути збільшення ширини буферів синхронізації. Конвеєрна робота блоку арбітраціі запитів до пам'яті дозволяє також конвейерізіровать щодо повільний блок кодування / декодування Хеммінга, що вимагає операції виключає АБО над 64 розрядами шини даних. Таким чином, досягається прозоре для комутатора виправлення помилок.

Запропонована архітектура має такі властивості:

· Дві мікросхеми ЗУ, встановлені паралельно, для забезпечення необхідної пропускної спроможності.

· Синхронізація даних різних доменів синхросигналов за допомогою буферів FIFO.

· Пакетна обробка для зменшення часу доступу / арбітраціі.

· Виправлення однобітових помилок / виявлення помилок в двох бітах за допомогою коду Хеммінга.

Мал. 3. Буфер FIFO, який використовується для запису даних в ЗУ

Представлене рішення використовує максимальну продуктивність компонента пам'яті SRAM. Для розробки комутатора з великою кількістю портів або підтримує більш швидкі технології (швидше, ніж 1 Гбіт / с) буде потрібно подальше збільшення пропускної здатності каналу звернення до пам'яті. При цьому використані підходи можуть виявитися невідповідними, і найбільш імовірним рішенням бачиться використання зовнішнього ЗУ типу DDR (II) SDRAM, що володіє більшою частотою роботи (для SRAM межею є 300 МГц), або використання інших технологій виробництва мікросхем, що дозволяють розташувати загальну пам'ять на кристалі комутатора .

Мал. 4. Синхронна пам'ять з нульовим циклом перемикання в порівняння

з традиційною пам'яттю

В роботі запропонована архітектура контролера інтерфейсу пам'яті, що забезпечує максимальне використання пам'яті SRAM при збереженні відносно невисоких частот роботи ядра мікросхеми комутатора. Така архітектура надає необхідний безперервний доступ декількох гігабітних каналів комутатора до ЗУ і дозволяє зменшити витрати на використання мікросхем пам'яті SRAM і розробку ВЧ інтерфейсу доступу до ЗУ.

1. Оліфер мережі. Принципи, технології, протоколи. - СПб. Пітер, 20с. мул.

2. Стандарт ISO 35.100 - Open systems interconnection // www. iso. org.

6. Altera Stratix Device Handbook, Altera Corporation.