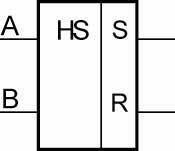

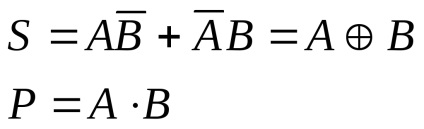

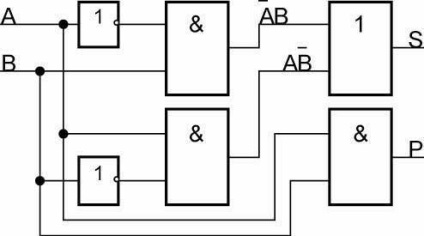

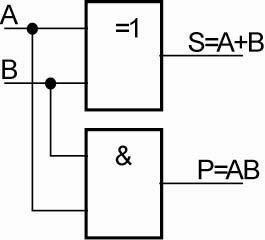

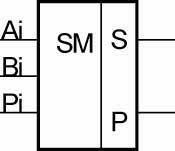

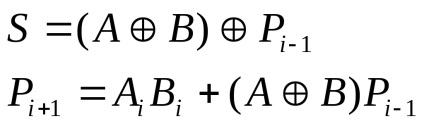

Робота полусумматора описується рівнянням:

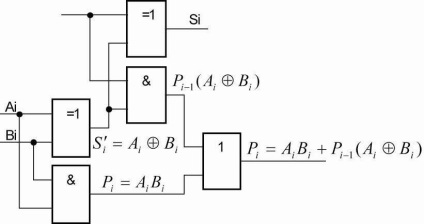

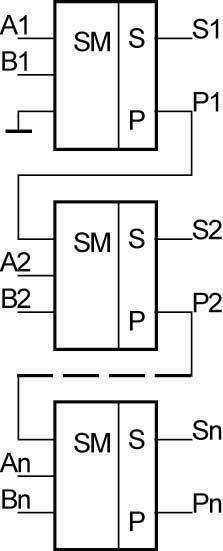

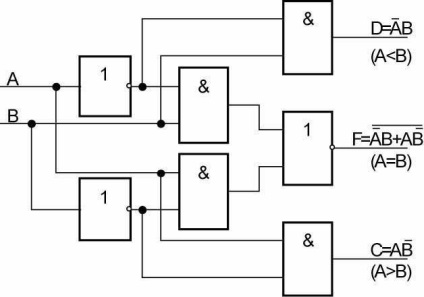

Логічна структура полусумматора в загальному і розгорнутому вигляді

HSімеет два входи і придатний тому для використання тільки в молодшому розряді. Пристрій для підсумовування двох багато розрядних чисел повинно мати, починаючи з другого розряду, три входи: два для доданків

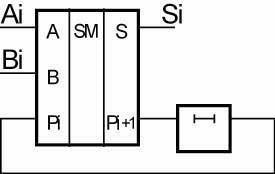

Повний суматор можна уявити як об'єднання двох полусумматора. Один служить для складання двох чисел, що належать одному розряду і забезпечує, вихід проміжної суми

При послідовному введенні використовуються один загальний для всіх розрядів повний суматор з додатковою ланцюгом затримки. Обидва доданків кодуються послідовностями імпульсів, які синхронно вводяться через входи AіB

н

Гідність - малі апаратні витрати.

Недолік - порівняно невисока швидкодія.

Число сумматоров n- розрядної паралельного суматора з послідовним переносом дорівнює числу розрядів.

В

складові

Швидкодія обмежена затримкою перенесення, поки сигнал перенесення з молодшого розряду не поширився по всій системі.

Час перенесення зменшується введення паралельного перенесення, який реалізується введенням блоків прискореного (наскрізного) перенесення.

Для кожного двійкового розряду додатково знаходяться два сигнали:

Процес формування прискореного перенесення описується наступними рівняннями:

Цифрові компаратори (пристрої порівняння)

Цифрові компаратори (compare- порівнювати) виконують порівняння двох чисел, заданих двійковим (двійковій - десятковим) коді.

Залежно від схемного виконання компаратори можуть визначати рівності або вид нерівності: A = B, A> BіліA> B, гдеAіB- незалежні числа з рівною кількістю розрядів. Результат порівняння відображається відповідним логічним рівням на виході.

Як правило, мікросхеми цифрових компараторів виконують всі ці операції і мають три виходи.

Для виявлення потрібного числа (слова) в потоці цифрової інформації.

Для позначки часу в годинних приладах.

Для виконання умовних переходів в обчислювальних пристроях.

Як однорозрядних компаратор може бути використана логічна схема, що виконує операцію еквівалентність (виключають АБО - НЕ). Найчастіше будується на базі "виключає - АБО".

Розгорнута логічна структура однорозрядного компаратора має вигляд:

при А> В (тобто А = 1, В = 0)

при А<В (т.е А=0, В=1)

Два n- розрядних двійкових числа рівні, коли попарно рівні між собою всі розряди цих чисел. Якщо чіслаAіB- чотирирозрядні, то ознакою рівності буде: A3 = B3; A2 = B2; A1 '= B1; A0 = B0, іліA = BпріF = F3F2F1F0 = 1, есліF = 0, тоA ≠ B.

Нерівність A> Bобеспечівается в одному з чотирьох випадках:

A3 = B3; A2 = B2; A1> B1;

A3 = B3; A2 = B2; A1 = B1; A0> B0.

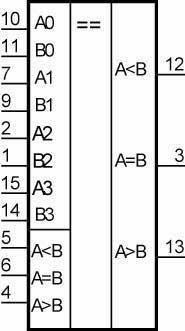

Прикладом цифрового компаратора може служити ІС К561ІП2.

Мікросхема має розширюють входи, які дозволяють нарощувати розрядність обох чисел без додаткових логічних елементів. (A = B, A> B, A> B)

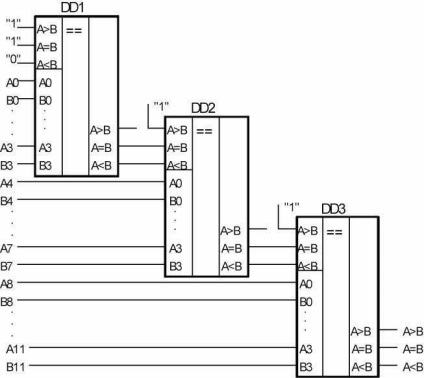

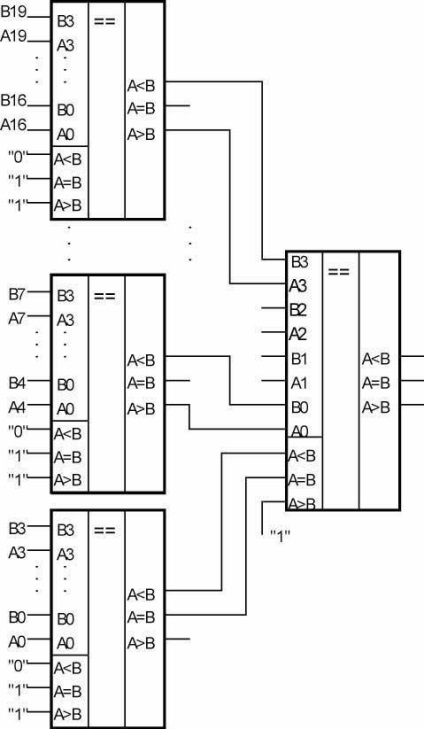

Компаратори можна з'єднувати каскадно і паралельно.

При паралельному (пірамідальному) з'єднанні час затримки менше (т. Е. Швидкодію компараторов вище.)

Каскадне включення цифрових компараторів:

Виходи A = BіA

Ця операція дозволяє підвищити надійність передачі двійкової інформації.

Простий і ефективний спосіб виявлення помилок заснований на припущенні, що в кожен момент часу помилка може виникнути тільки в одному розряді, і проявляється вона в зайвої одиниці або у втраті одиниці.

Т. о. якщо передане слово містить парне число одиниць в усіх розрядах, а на кінці лінії передачі це число виявиться непарною, значить, з'явилася помилка.

Реалізація цього методу здійснюється за допомогою спеціальних схем контролю парності.

На основі інформації на виході попереднього елемента схема формує додатковий біт (паритетний або контрольний біт), т. Е. "1" або "0" який додається до вихідної інформації.

Призначення паритетного біта - доводити число одиниць в кожному переданому слові до парного або непарного в залежності від прийнятої системи кодування.

На приймальному кінці лінії відбувається перевірка паритету (parity- відповідність). Якщо він правильний дозволяється прийом, якщо немає - відбувається включення сигналізатора помилок.

Паритет може бути парними і непарними.

У разі непарного паритету - сума одиниць разом з контрольним бітом - повинна бути непарною, а для парного - навпаки. На практиці непарний паритет використовується частіше, так як контроль непарності дозволяє фіксувати повне зникнення інформації.

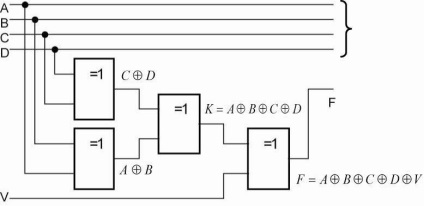

Структура схема перевірки парності - багатоступенева. У першій ступені (ярусі) попарно підсумовуються всі біти слова. Вихідні сигнали першого ярусу є вхідними для другого і так далі послідовно до закінчення визначення парності або непарності всього слова.

Отриманий результат на останньому етапі порівнюється з контрольним сигналом, що задає вид використовуваного паритету.

Якщо паритет парний, т. Е. Число одиниць в слові, включаючи паритетний біт, має бути парним, то контрольний сигнал повинен дорівнювати сумі по модулю 2 всіх інформаційних розрядів слова. Для непарного паритету контрольний сигнал є інверсією зазначеної суми.

Т. е. Незалежно від паритету чотирьох розрядного слова ABCDпарітет пятіразрядний кодаABCDFбудет завжди однаковий.

Потенціал на вході Vопределяет вид використовуваного паритету.

Прикладом самостійних виробів можуть служити КМОП ІС К561СА1 і ТТЛ К155ІП2.