Арифметичний пристрій - одне з головних пристроїв цифрової електронної обчислювальної машини, в якому виконуються логічні і арифметичні операції над числами.

Здійснення будь-якої логічної або арифметичної операції в арифметичному пристрої зводиться, в кінцевому рахунку, до послідовного виконання декількох микроопераций або елементарних операцій: установка в «нуль» будь-яких розрядів блоків арифметичного пристрою, прийом окремого розряду або коду числа, зрушення в бік старших або молодших розрядів числа , отримання інверсного (зворотного) коду, складання кодів, видача коду і т. д.

До арифметичним операціям можна віднести складання, добування кореня, множення, ділення і віднімання. Розподіл і добування кореня, а також зведення числа в ступінь, визначення тригонометричних функцій, логарифмів і т. П. Вельми часто здійснюються за стандартними підпрограм. Головна операція цифрової обчислювальної машини - складання, до якого зводяться всі інші арифметичні операції. Наприклад, множення зводиться до підсумовування кілька разів множимо; поділ - до почергового знаходженню цифр приватного за допомогою вирахування і складання.

Арифметичний пристрій в складі цифрової обчислювальної машини пов'язано з центральним пристроєм управління. З запам'ятовує надходять початкові числа, по команді центрального пристрою управління ( «помножити», «відняти», «скласти» і т. Д.). Арифметичний пристрій виробляє відповідні операції, після чого результати операцій знову передаються в пристрій. а сигнали, які означають закінчення операції, показники переповнення розрядної сітки і т. п. при необхідності передаються в центральний пристрій управління.

Головні характеристики і склад арифметичного пристрою залежать від необхідної швидкодії, розрядності чисел, обраної системи числення, алгоритмів виконання операцій і їх прискорення, типу застосовуваних схем і зв'язків між ними (імпульсно-потенційні, імпульсні або потенційні) і форми подання чисел.

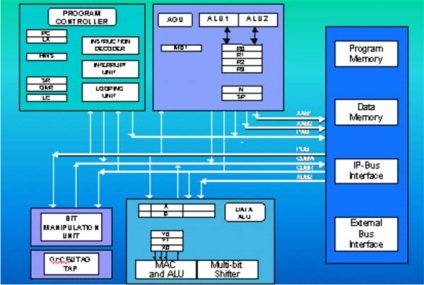

Арифметичний пристрій, як правило, складається з декількох регістрів для нетривалого зберігання чисел, логічних ланцюгів, призначених для виконання найпростіших операцій над числами, суматорів і місцевого пристрою управління, яке сприймає команду на твір операції від центрального пристрою управління машини і що відпрацьовує потрібну послідовність команд.

Залежно від використовуваного способу підсумовування чисел розрізняють арифметичні пристрої послідовно-паралельного, паралельного і послідовного дії. В арифметичних пристроях послідовної дії підсумовування двох чисел здійснюється однорозрядним сумматором, через який поетапно, починаючи з молодших, проходять всі наявні розряди доданків. В арифметичних пристроях паралельного дії всі розряди кожного з доданків подаються в суматор одночасно, кількість розрядів суматора дорівнює кількості розрядів в доданків.

Арифметичні пристрої послідовно-паралельної дії є проміжною формою. Регістри паралельного арифметичного пристрою складаються з тригерів або подібних елементів і дозволяють зробити одночасний доступ до всіх розрядів числа. В арифметичному пристрої послідовного дії замість регістрів застосовуються в тому числі і лінії затримки, які, в разі необхідності, замикаються в кільце через логічні ланцюги рециркуляції і підсилювачі. В елементах і схемах арифметичного пристрою застосовуються електронні лампи (в початкових зразках), напівпровідникові діоди, транзистори. феррит-діодні осередки і ферит-транзисторні осередку.

В арифметичних пристроях з мікропрограмного управлінням у складі місцевого пристрою управління використовують також ферритові матриці, призначені для зберігання мікропрограм операцій.

Основні вимоги до елементів схем арифметичного пристрою - висока надійність. технологічність, взаємозамінність однотипних елементів, повторюваність основних параметрів у виробництві.

З урахуванням способу кодування чисел арифметичні пристрої виробляються для операцій в десяткового або двійковій системі, рідше - в троичной, або який-небудь іншій системі числення, з різною кількістю розрядів, з числами, представленими у формі з плаваючою або з фіксованою комою, або і з тими і з іншими.

Методи прискорення виконання операцій використовуються або в елементарних операціях, або в повних операціях арифметичного пристрою. Особливо результативно прискорення елементарної операції підсумовування, тому що вона здебільшого входить в алгебраїчне додавання або віднімання, ділення, множення і ін.

У послідовних арифметичних пристроях прискорення підсумовування виходить переходом до послідовно-паралельним схемами; відповідно в паралельних - використанням схем, які використовують статистичний характер перенесень, схем «з миттєвим переносом» і т. п. Найбільш вивчені методи прискорення множення. У послідовних пристроях вони базуються головним чином на введенні додаткових суматорів, які дозволяють одночасно підсумовувати кілька часткових творів; в межі наявність п сумматоров послідовного типу (або п / 2 логічних схем і суматорів) дозволяє зробити множення за 2п тактів. У паралельних арифметичних пристроях використовуються методи прискорення множення апаратні і логічні 1-го і 2-го порядку. Логічні методи базуються на модифікації множника; збільшення кількості апаратури при їх застосуванні стосується тільки місцевого пристрою управління і не залежить від числа розрядів в перемножуєте числах; практичний і теоретичний межа можливостей логічних методів - зменшення середнього числа підсумовування при здійсненні одного множення до 1/3 на кожен двійковий розряд множника. Апаратні методи 1-го порядку базуються на введенні допоміжних сумматоров, допоміжних ланцюгів запам'ятовування перенесень або заміщення ланцюгів зсуву ланцюгами ділення і множення на особливі множники; кількість допоміжного обладнання пропорційно кількості розрядів; число тактів підсумовування в процесі множення трансцендентно може бути зменшено до одного (незалежно від числа розрядів множника), проте в дійсності ця межа не можна досягти. Апаратні методи 2-го порядку базуються на побудові пірамід суматорів; обсяг обладнання пропорційний квадрату кількості розрядів, час множення рівносильно 2-3 тактів підсумовування. Подібні методи розробляються для прискорення операції ділення.

Головні тенденції в розвитку арифметичних пристроїв пов'язані з використанням мікроелектроніки. Внаслідок чого застосовуються матричні схеми для прямого підсумовування і множення десяткових цифр, паралель-но-паралельні і надпаралельні суматори, апаратні методи 2-го порядку для прискорення ділення і множення, іншими словами, побудови з великим числом повторюваних елементів і систематичними зв'язками між ними. Шукаються також нові способи кодування чисел, які спрощують виконання операцій, інші методи прискорення операцій, виправлення помилок і апаратного контролю. При цьому ставляться цілі підвищення швидкодії, збільшення надійності, зменшення вартості споживаної потужності і габаритів.