При реалізації мікропроцесорів традиційно використовується два підходи до побудови архітектури:

- Архітектура фон Неймана

- Гарвардська архітектура

В архітектурі фон Неймана застосовується однорідна пам'ять мікропроцесора. У цю пам'ять можуть записуватися різні програми. При цьому спеціальна програма-завантажувач працює з ними як з даними. Потім управління може бути передано цими програмами і вони вже починають виконувати свій алгоритм. При подібному підході до управління мікропроцесором вдається досягти максимальної гнучкості мікропроцесорної системи.

Як недолік архітектури фон Неймана можна назвати можливість ненавмисного порушення працездатності системи (програмні помилки) і навмисне знищення її роботи (вірусні атаки). В Гарвардської архітектури принципово різняться два виду пам'яті мікропроцесора:

- Пам'ять програм (для зберігання інструкцій мікропроцесора)

- Пам'ять даних (для тимчасового зберігання і обробки змінних)

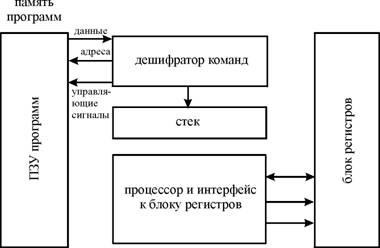

У гарвардській архітектурі принципово неможливо здійснити операцію запису в пам'ять програм, що виключає можливість випадкового руйнування керуючої програми в разі помилки програми при роботі з даними або атаки третіх осіб. Крім того, для роботи з пам'яттю програм і з пам'яттю даних організуються окремі шини обміну даними (системні шини), як це показано на малюнку 1.

Малюнок 1. Структурна схема гарвардської архітектури

Ці особливості визначили сфери застосування гарвардської архітектури. Гарвардська архітектура застосовується в мікроконтролер і в сигнальних процесорах. де потрібно забезпечити високу надійність роботи апаратури. У сигнальних процесорах Гарвардська архітектура доповнюється застосуванням трехшінного операційного блоку мікропроцесора. Трехшінная архітектура операційного блоку дозволяє поєднати операції зчитування двох операндів із записом результату виконання команди в оперативну пам'ять мікропроцесора. Це значно збільшує продуктивність сигнального мікропроцесора без збільшення його тактової частоти.

Модифікована гарвардська структура застосовується в сучасних мікросхемах сигнальних процесорів. Ще далі по шляху зменшення вартості кристала за рахунок зменшення площі, займаної системними шинами пішли виробники однокрісталльних ЕОМ - мікроконтролерів. У цих мікросхемах застосовується одна системна шина для передачі команд і даних (модифікована Гарвардська архітектура) і всередині кристалу.

У сигнальних процесорах для реалізації таких алгоритмах як швидке перетворення Фур'є і цифрова фільтрація часто потрібно ще більшу кількість внутрішніх шин. Зазвичай застосовуються дві шини для читання даних, одна шина для запису даних і одна шина для читання інструкцій. Подібна структура мікропроцесора отримала назву розширеної гарвардської архітектури. Цей підхід практикують виробники сигнальних процесорів - фірми Analog Devices (сімейства сигнальних процесорів BlackFin і Tiger Shark), Texas Instrunents (сімейства сигнальних процесорів C5000 ™ DSPs і C6000 ™ DSPs), Freescale (сімейства сигнальних процесорів MSC8251 і DSP56K).

Разом зі статтею "Гарвардська архітектура і її гідності" читають: