Е

Мал. 73. Модифікація ОС-3.

Мал. 74. Побудова ланцюга прискореного перенесення.

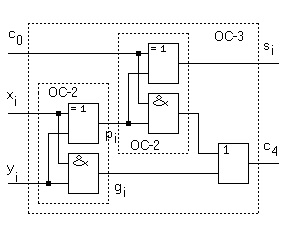

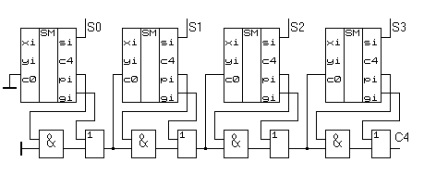

В останньому вираженііgi - з'являється тоді, коли перенесення в даному розряді визначається комбінацією вхідних змінних. Поетомуgi - називають функцією генерації перенесення. Переменная-- вказує, чи передається перенесення, отриманий в молодшому розряді, далі і називається функцією поширення перенесення. Останній вираз показує, що для схемотехнической реалізації перенесення необхідні два елементи: 2 І і 2ИЛИ. Побудова ланцюга прискореного перенесення для четирёхразрядного сумматора показано на ріс.74. На малюнку не відображені ланцюга задання вхідних змінних, а тільки показано побудова ланцюга прискореного перенесення. Молодший розряд знаходиться зліва. При великої розрядності операндів ланцюг прискореного перенесення дозволяє істотно підвищити швидкодію сумматоров.

Арифметико-логічний пристрій.

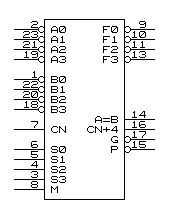

З метою збільшення функціональних можливостей обчислювальних блоків ЕОМ були розроблені електронні комбінаційні пристрої дозволяють виконувати певний набір арифметичних і логічних операцій. Ці пристрої отримали назву - арифметико-логічні пристрої (АЛП). У ТТЛ серіях АЛУ отримали шифр - ХХХІП3. На ріс.75 наведено зображення АЛУ. Як видно на малюнку, операції проводяться над четирёхразряднимі операндами А і В, результат отримуємо на виходах F. Мікросхема має п'ять керуючих входів - S і M, і відповідно виконує 32 арифметичних і логічних операцій. Арифметичні операції виконуються пословно, тобто з урахуванням переносів і позичок, а логічні операції виконуються побитно. Є вхід переносу з молодшого розряду CN і вихід перенесення в старший розряд CN + 4, що дозволяє будувати багаторозрядні схеми АЛУ з кількістю розрядів кратним чотирьом. При виконанні арифметичних операцій формуються вихідні змінні G і P, що дозволяє при використанні декількох мікросхем будувати схему з прискореним переносом. Крім того, є вихід А = В, сигнал на цьому виході активний при рівності операндів.