Однією з найважливіших особливостей будь-якої мікросхеми, що визначає її функціональні можливості і особливості застосування є спосіб виконання вихідного каскаду. Найбільш часто використовуються чотири типи вихідних каскадів:

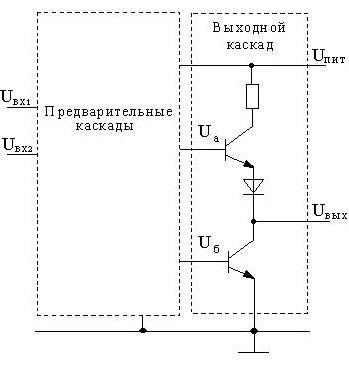

1. Стандартний вихідний каскад.

Схема реалізована так, що напруги Uа і Uб завжди змінюються в протифазі. Це означає, що в парі транзисторів вихідного каскаду завжди один закритий, а другий відкритий.

Такий вихідний каскад забезпечує великий вихідний (впадає) струм при логічному 0 на виході (I 0 вих), коли відкритий нижній транзистор, і значно менший вихідний (що випливає) струм при логічної 1 на виході (I 1 вих), коли відкритий верхній транзистор.

Оскільки така схема вихідного каскаду є стандартною, то на її умовно-графічному позначенні це ніяк не позначається.

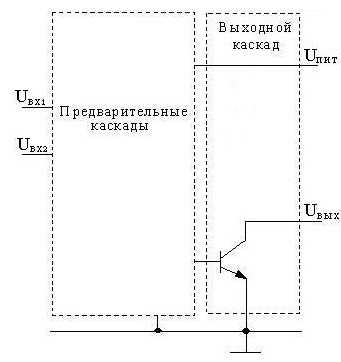

2. Вихідний каскад з відкритим колектором.

У такій схемі в якості вихідного каскаду використовується транзистор, колектор якого не підключений до джерела живлення, а підключений тільки до зовнішнього висновку мікросхеми, тому її вихід повинен бути підключений за допомогою зовнішнього резистора до відповідного джерела живлення. Транзистори вихідного каскаду можуть бути розраховані на різний допустима напруга живлення, відмінне від напруги харчування решти схеми.

Вихідний каскад з відкритим колектором забезпечує великий вихідний (впадає) струм при логічному нулі на виході (I 0 вих).

На умовно-графічному позначенні такі мікросхеми мають позначку à .

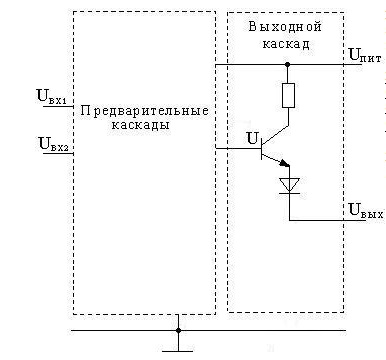

3. Вихідний каскад з відкритим емітером.

У такій схемі колектор підключений всередині мікросхеми звичайним чином, а емітер не підключений до загального проводу, а з'єднаний тільки з одним із зовнішніх висновків.

Навантаження до таких мікросхем підключається між висновками емітера і загальним проводом, тобто вихідний каскад буде являти собою емітерний повторювач, що забезпечує великий вихідний (що випливає) струм при логічної 1 на виході (I 1 вих).

На умовно-графічному позначенні такі мікросхеми мають позначку `à.

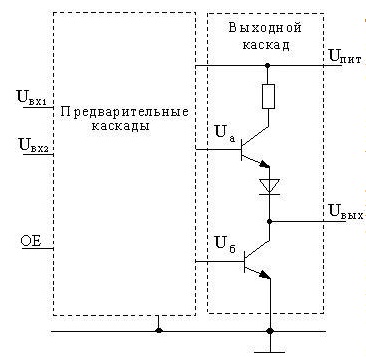

4.Схема з трьома станами на виході.

Дана схема відрізняється від схеми зі стандартним виходом тим, що в ній напруги Uа і Uб можуть бути як в протифазі (тоді вона працює як схема зі стандартним виходом), так і у фазі, коли обидва напруги Uа іUб приймають низький (закриває) рівень, що унеможливлює протікання вихідних струмів через транзистори. Фактично це рівнозначно станом, коли висновок виходу мікросхеми відключений від решти її частини. У цьому випадку говорять, що вихід знаходиться в третьому стані (високоімпедансних, високоомному, z-стані).

Управління переходом виходу зі стандартного режиму в третій стан здійснюється спеціальним керуючим сигналом OE (Output Enable - дозвіл виходу). На умовно-графічному позначенні такі мікросхеми позначаються à (Або Z).

11. Об'єднання виходів цифрових мікросхем

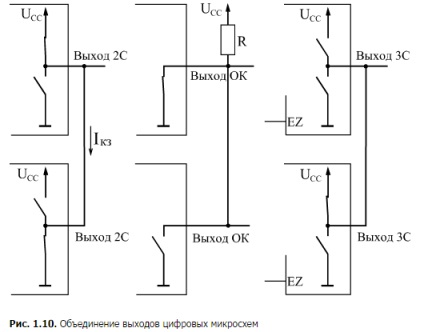

Нарешті, вихід з трьома станами 3С дуже схожий на стандартний вихід. але до двох станів додається ще й третє - пасивне, в якому вихід можна вважати відключеним від такої схеми. На першому і другому рівнях уявлення такойвиход можна вважати складається з двох перемикачів (рис. 1.9), які можуть замикатися по черзі, даючи логічний нуль і логічну одиницю, але можуть і розмикатися одночасно. Це третій стан називається також високоімпедансним або Z-станом. Для перекладу виходу до третього Z-стан використовується спеціальний керуючий вхід, що позначається OE (Output Enable - дозвіл виходу) або EZ (Enable Z-state).

При об'єднанні двох або більше виходів 2С цілком можлива ситуація, при якій один вихід прагне видати сигнал логічної одиниці, а інший - сигнал логічного нуля. Легко помітити, що в цьому випадку через верхній замкнутий ключ виходу, що видає одиницю, і через нижній замкнутий ключ виходу, що видає нуль, піде неприпустимо великий струм короткого замикання Iкз. Це аварійна ситуація, при якій рівень одержуваного вихідного логічного сигналу точно не визначений - він може сприйматися подальшим входом і як нуль, і як одиниця. Конфліктуючі виходи можуть навіть вийти з ладу, порушивши роботу мікросхем і схеми в цілому.

Зате в разі об'єднання двох виходів ОК такого конфлікту в принципі відбутися не може. Навіть якщо ключ одного виходу замкнутий, а іншого - розімкнути, аварійної ситуації не відбудеться, тому що неприпустимо великого струму не буде, а на об'єднаному виході буде сигнал логічного нуля. А при об'єднанні двох виходів 3С аварійна ситуація хоч і можлива (якщо обидва виходи одночасно знаходяться в активному стані), але її легко можна запобігти, якщо організувати схему так, що в активному стані завжди буде знаходитися тільки один з об'єднаних виходів 3С.

Об'єднання виходів цифрових мікросхем абсолютно необхідно також при шинної (або, як ще кажуть, магістральної) організації зв'язків між цифровими пристроями. Шинна організація зв'язків застосовується, наприклад, в комп'ютерах і в другіхмікропроцессорних системах. Суть її зводиться до наступного.

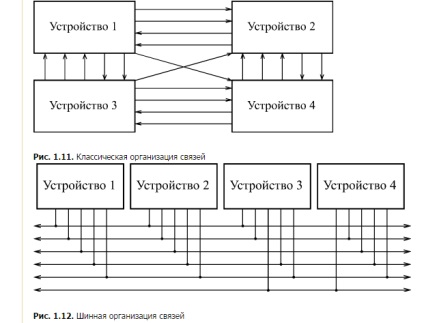

При класичної організації зв'язків (рис. 1.11) всі сигнали між пристроями передаються за своїми окремими лініями (проводах). Кожен пристрій передає свої сигнали всім іншим незалежно від інших пристроїв. В цьому випадку зазвичай виходить дуже багато ліній зв'язку, до того ж правила обміну сигналами по цим лініям (або протоколи обміну) надзвичайно різноманітні.

При шинної ж організації зв'язків (рис. 1.12) всі сигнали між пристроями передаються по одним і тим же лініях (проводах), але в різні моменти часу (це називається тимчасовим мультиплексированием). В результаті кількість ліній зв'язку різко скорочується, а правила обміну сигналами істотно спрощуються. Група ліній (сигналів), яка використовується декількома пристроями, як раз і називається шиною. Зрозуміло, що об'єднання виходів в цьому випадку абсолютно необхідно - адже кожен пристрій має мати можливість видавати свій сигнал на загальну лінію. До недоліків шинної організації відноситься перш за все невисока (у порівнянні з класичною структурою зв'язків) швидкість обміну сигналами. При простих структурах зв'язку вона може бути надлишкова.

Але повернемося до типам виходів цифрових мікросхем.

На третьому рівні уявлення (електрична модель) необхідно вже враховувати, що вихідні ключі (рис. 1.9) являють собою не прості тумблери (як на перших двох рівнях уявлення), а транзисторні ключі зі своїми специфічними параметрами. Однак в більшості випадків досить знати, який струм може видати даний вихід при логічному нулі (IOL) і при логічній одиниці (IOH). Величини цих струмів не повинні перевищувати суми струмів всіх входів, підключених до цього виходу (відповідно IIL і IIH). Кількістю входів, яке можна підключити до одного виходу, визначається коефіцієнт розгалуження або навантажувальну здатність мікросхеми. Існують мікросхеми зі звичайною навантажувальною здатністю і з підвищеною здатністю навантаження (більше звичайної в два рази і більше). Виходи 3С, як правило, мають підвищену навантажувальну здатність (тобто забезпечують великі вихідні струми). Виходи 2С і ОК можуть бути як зі звичайною, так і з підвищеною здатністю навантаження.

Також на третьому рівні уявлення (електрична модель) необхідно враховувати видаються виходом мікросхеми величини вихідних напруг UOL і UOH. Виходи ОК можуть бути розраховані як на звичайне вихідна напруга логічної одиниці (UOH = UCC = 5 В), так і на підвищену напругу логічної одиниці (до 30 В). В останньому випадку зовнішній резистор цього виходу (див. Рис. 1.9) підключається до джерела підвищеної напруги.

Тільки в складних випадках, наприклад, при перекладі логічного елемента в лінійний режим за рахунок зворотних зв'язків, потрібен облік інших параметрів вхідних і вихідних каскадів. Але в цих рідкісних випадках набагато простіше і надійніше не брати до уваги нічого самому, а скористатися стандартними схемами включення мікросхем або підібрати режими роботи і номінали зовнішніх елементів (резисторів, конденсаторів) безпосередньо на макеті проектованого пристрою. На відміну від розрахунків, такий підхід дасть повну гарантію працездатності обраного рішення.